## TCM4300 Data Manual

Advanced RF Cellular Telephone Interface Circuit (ARCTIC™)

SLWS010G February 1998

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

## **Contents**

| Se | ction |          | Title                                                             | Page  |

|----|-------|----------|-------------------------------------------------------------------|-------|

| 1  | Intro | ductio   | n                                                                 | . 1–1 |

|    | 1.1   |          | res                                                               |       |

|    | 1.2   |          | 300 Functional Block Diagram                                      |       |

|    | 1.3   |          | signments                                                         |       |

|    | 1.4   |          | nal Functions                                                     |       |

| 2  | Elec  | trical S | Specifications                                                    | . 2–1 |

|    | 2.1   |          | ate Maximum Ratings Over Operating Free-Air Temperature Range     |       |

|    | 2.2   |          | ation Rating Table                                                |       |

|    | 2.3   |          | nmended Operating Conditions                                      |       |

|    | 2.4   |          | cal Characteristics Over Full Range Of Operating Conditions       |       |

|    |       | 2.4.1    | Power Consumption                                                 | . 2–2 |

|    |       | 2.4.2    | Reference Characteristics                                         | . 2–2 |

|    |       | 2.4.3    | Terminal Impedance                                                |       |

|    |       | 2.4.4    | RXIP, RXIN, RXQP, and RXQN Inputs (AVDD = 3 V, 4.5 V, 5 V)        |       |

|    |       | 2.4.5    | Transmit I and Q Channel Outputs                                  |       |

|    |       | 2.4.6    | Auxiliary D/A Converters                                          |       |

|    |       | 2.4.7    | Auxiliary D/A Converters Slope (AGC, AFC, PWRCONT)                |       |

|    |       | 2.4.8    | Auxiliary D/A Converters Slope (LCDCONTR)                         |       |

|    |       | 2.4.9    | RSSI/Battery A/D Converter                                        |       |

|    | 2.5   |          | ting Characteristics Over Full Range of Operating Conditions      | . 2–6 |

|    |       | 2.5.1    | Receive (RX) Channel Frequency Response                           | 0.0   |

|    |       | 0.50     | (RXI, RXQ Input in Digital Mode)                                  | . 2–6 |

|    |       | 2.5.2    | Receive (RX) Channel Frequency Response (FM Input in Analog Mode) | 2.6   |

|    |       | 2.5.3    | Transmit (TX) Channel Frequency Response (Digital Mode)           |       |

|    |       | 2.5.4    | Transmit (TX) Channel Frequency Response (Analog Mode)            |       |

| 3  | Dave  |          | Measurement Information                                           |       |

| 3  | 3.1   |          | OUT Timing Requirements                                           |       |

|    | 3.1   |          | 300 to Microcontroller Interface Timing Requirements              | . 5–1 |

|    | 5.2   |          | bishi Read Cycle)                                                 | 3_2   |

|    | 3.3   |          | 300 to Microcontroller Interface Timing Requirements              | . 02  |

|    | 0.0   |          | bishi Write Cycle)                                                | 3–3   |

|    | 3.4   |          | 300 to Microcontroller Interface Timing Requirements              |       |

|    | • • • |          | Read Cycle)                                                       | . 3–4 |

|    | 3.5   | TCM4     | 300 to Microcontroller Interface Timing Requirements              |       |

|    |       |          | Vrite Cycle))                                                     | . 3–5 |

|    | 3.6   |          | 300 to Microcontroller Interface Timing Requirements              |       |

|    |       |          | rola 16-Bit Read Cycle)                                           | . 3–6 |

|    | 3.7   | TCM4     | 300 to Microcontroller Interface Timing Requirements              |       |

|    |       | (Moto    | rola 16-Bit Write Cycle)                                          | 3–7   |

|    | 3.8   |          | 300 to Microcontroller Interface Timing Requirements              |       |

|    |       | (Motor   | ola 8-Bit Read Cycle)                                             | 3–8   |

|   | 3.9   | TCM4300 to Microcontroller Interface Timing Requirements (Motorola 8-Bit Write Cycle) | 3_0         |

|---|-------|---------------------------------------------------------------------------------------|-------------|

|   | 3 10  | Switching Characteristics, TCM4300 to DSP Interface (Read Cycle)                      | ე_ე<br>ვ_1∩ |

|   |       | Switching Characteristics, TCM4300 to DSP Interface (Write Cycle)                     |             |

|   | 0.11  | ownering characteristics, rowi-soc to bor interface (write cycle)                     | 5 11        |

| 4 | Princ | ciples of Operation                                                                   | 4–1         |

|   | 4.1   | Data Transfer                                                                         | 4–1         |

|   | 4.2   | Receive Section                                                                       | 4–1         |

|   | 4.3   | Transmit Section                                                                      |             |

|   | 4.4   | Transmit Burst Operation (Digital Mode)                                               | 4–5         |

|   | 4.5   | Transmit I And Q Output Level                                                         | 4–7         |

|   | 4.6   | Wide-Band Data Demodulator                                                            | 4–7         |

|   | 4.7   | Wide-band Data Interrupts                                                             | 4–8         |

|   | 4.8   | Wide-band Data Demodulator General Information                                        | 4–9         |

|   | 4.9   | Auxiliary DACs, LCD Contrast Converter                                                | 4–10        |

|   | 4.10  | RSSI, Battery Monitor                                                                 | 4–11        |

|   | 4.11  | Timing And Clock Generation                                                           | 4–11        |

|   |       | 4.11.1 Clock Generation                                                               | 4–12        |

|   |       | 4.11.2 Speech-Codec Clock Generation                                                  | 4–12        |

|   |       | 4.11.3 Microcontroller Clock                                                          | 4–12        |

|   |       | 4.11.4 Sample Interrupt SINT                                                          | 4–12        |

|   |       | 4.11.5 Phase-Adjustment Strategy                                                      |             |

|   | 4.12  | Frequency Synthesizer Interface                                                       | 4–15        |

|   |       | Power Control Port                                                                    |             |

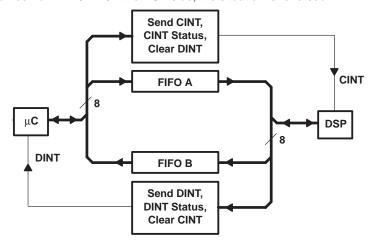

|   |       | Microcontroller-DSP Communications                                                    |             |

|   | 4.15  | Microcontroller Register Map                                                          | 4–21        |

|   |       | Wide-Band Data/Control Register                                                       |             |

|   |       | Microcontroller Status and Control Registers                                          |             |

|   |       | LCD Contrast                                                                          |             |

|   | 4.19  | DSP Register Map                                                                      | 4–25        |

|   |       | Wide-Band Data Registers                                                              |             |

|   |       | Base Station Offset Register                                                          |             |

|   |       | DSP Status and Control Registers                                                      |             |

|   |       | Reset                                                                                 |             |

|   |       | 4.23.1 Power-On Reset                                                                 |             |

|   |       | 4.23.2 Internal Reset State                                                           |             |

|   | 4.24  | Microcontroller Interface                                                             |             |

|   |       | 4.24.1 Intel Microcontroller Mode Of Operation                                        |             |

|   |       | 4.24.2 Mitsubishi Microcontroller Mode of Operation                                   |             |

|   |       | 4.24.3 Motorola Microcontroller Mode of Operation                                     |             |

|   |       |                                                                                       |             |

| 5 | Mec   | hanical Data                                                                          | 5–1         |

## **List of Illustrations**

| Figure       | Title                                                                                                                       | Page |

|--------------|-----------------------------------------------------------------------------------------------------------------------------|------|

| 3–1          | MCLKOUT Timing Diagram                                                                                                      | 3–1  |

| 3–2          | Microcontroller Interface Timing Requirements (Mitsubishi Configuration Read Cycle, MTS [1:0] = 10)                         |      |

| 3–3          | Microcontroller Interface Timing Requirements (Mitsubishi Configuration Write Cycle, MTS [1:0] = 10)                        | 3–3  |

| 3–4          | Microcontroller Interface Timing Requirements (Intel Configuration Read Cycle, MTS [1:0] = 00)                              |      |

| 3–5          | Microcontroller Interface Timing Requirements (Intel Configuration Write Cycle, MTS [1:0] = 00)                             | 3–5  |

| 3–6          | Microcontroller Interface Timing Requirements (Motorola 16-Bit Read Cycle, MTS [1:0] = 10)                                  |      |

| 3–7          | Microcontroller Interface Timing Requirements  (Motorola 16-Bit Write Cycle, MTS [1:0] = 10)                                |      |

| 3–8          | Microcontroller Interface Timing Requirements                                                                               |      |

| 3–9          | (Motorola 8-Bit Read Cycle, MTS [1:0] = 01)                                                                                 |      |

| 3–10<br>3–11 | (Motorola 8-Bit Write Cycle, MTS [1:0] = 01)  TCM4300 to DSP Interface (Read Cycle)  TCM4300 to DSP Interface (Write Cycle) | 3-10 |

| 4–1          | Residual (Uncorrectable) Offset Error and Zero Code Error, I to Q                                                           |      |

| 4–2<br>4–3   | Power Ramp-Up/Ramp-Down TIming Diagram                                                                                      |      |

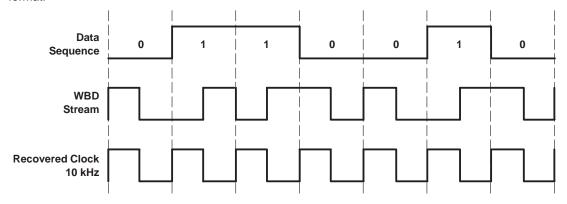

| 4–4          | WBD Manchester-Coded Data Stream                                                                                            |      |

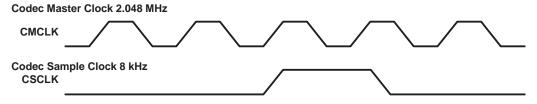

| 4–5          | Codec Master and Sample Clock Timing                                                                                        |      |

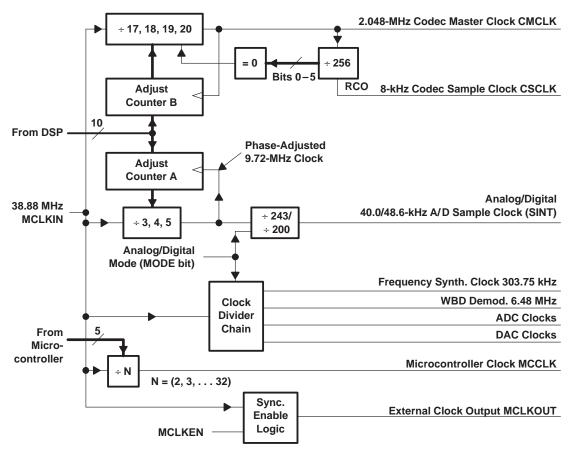

| 4–6          | Timing and Clock Generation for 38.88-MHz Clock                                                                             |      |

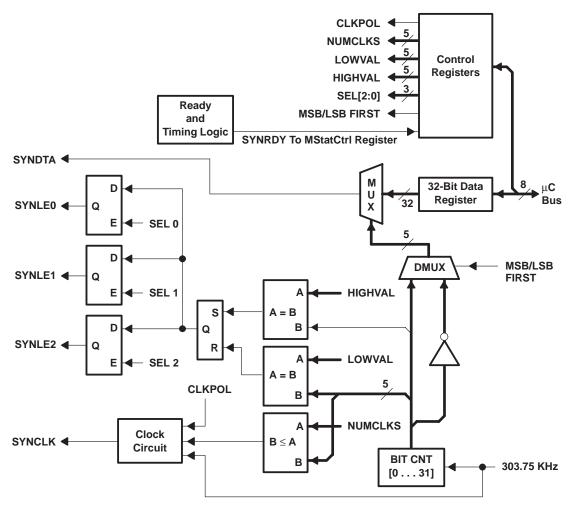

| 4–7          | Synthesizer Interface Circuit Block Diagram                                                                                 | 4-16 |

| 4–8          | Contents of SynData Registers                                                                                               | 4–17 |

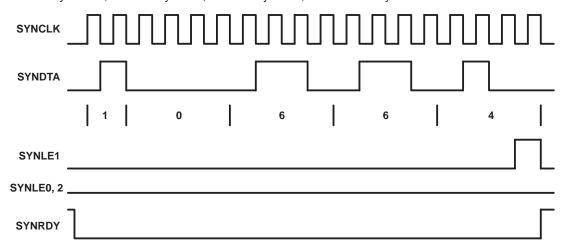

| 4–9          | Example Synthesizer Output                                                                                                  | 4–18 |

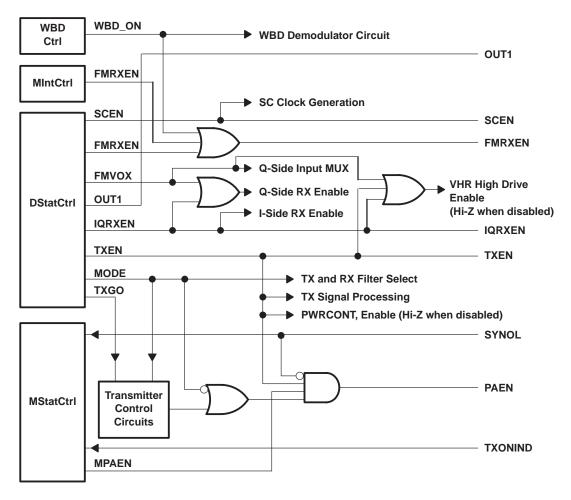

| 4–10         | Internal and External Power Control Logic                                                                                   |      |

| 4–11         | Microcontroller-DSP Data Buffers                                                                                            | 4–20 |

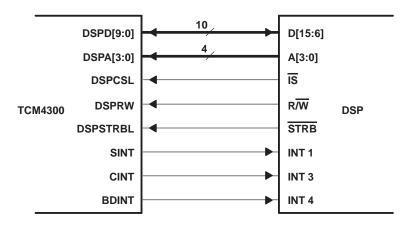

| 4–12         | DSP Interface                                                                                                               |      |

| 4–13         | Power-On Reset Timing                                                                                                       | 4-28 |

## **List of Tables**

| Table | Title                                                                      | Page |

|-------|----------------------------------------------------------------------------|------|

| 4-1   | TCM4300 Receive Channel Control Signals                                    | 4–1  |

| 4–2   | RXIP, RXIN, RXQP, and RXQN Inputs (AV <sub>DD</sub> = 3 V, 4.5 V, 5 V)     | 4–2  |

| 4–3   | Receive (RX) Channel Frequency Response (FM Input in Analog Mode)          |      |

| 4–4   | Receive (RX) Channel Frequency Response (RXI, RXQ Input in Digital Mode) . | 4–3  |

| 4–5   | Transmit (TX) I and Q Channel Outputs                                      |      |

| 4–6   | Transmit (TX) Channel Frequency Response (Digital Mode)                    | 4–5  |

| 4–7   | Transmit (TX) Channel Frequency Response (Analog Mode)                     | 4–5  |

| 4–8   | Typical Bit-Error-Rate Performance (WBD_BW = 000)                          |      |

| 4–9   | Bits in Control Register WBDCtrl                                           | 4–8  |

| 4–10  | Auxiliary D/A Converters                                                   |      |

| 4–11  | Auxiliary D/A Converters Slope (AGC, AFC, PWRCONT)                         |      |

| 4–12  | Auxiliary D/A Converters Slope (LCDCONTR)                                  | 4–11 |

| 4–13  | RSSI/Battery A/D Converter                                                 |      |

| 4–14  | Synthesizer Control Fields                                                 |      |

| 4–15  | External Power Control Signals                                             |      |

| 4–16  | Microcontroller Register Map                                               |      |

| 4–17  | Microcontroller Register Definitions                                       |      |

| 4–18  | WBDCtrl Register                                                           |      |

| 4–19  | MStatCtrl Register Bits                                                    |      |

| 4–20  | DSP Register Map                                                           |      |

| 4–21  | DSP Register Definitions                                                   |      |

| 4–22  | DStatCtrl Register Bits                                                    |      |

| 4–23  | Power-On Reset Register Initialization                                     |      |

| 4–24  | Microcontroller Interface Configuration                                    |      |

| 4–25  | Microcontroller Interface Connections for Intel Mode                       |      |

| 4–26  | Microcontroller Interface Connections for Mitsubishi Mode                  |      |

| 4–27  | Microcontroller Interface Connections for Motorola Mode (8 bits)           |      |

| 4–28  | Microcontroller Interface Connections for Motorola Mode (16 bits)          | 4–31 |

#### 1 Introduction

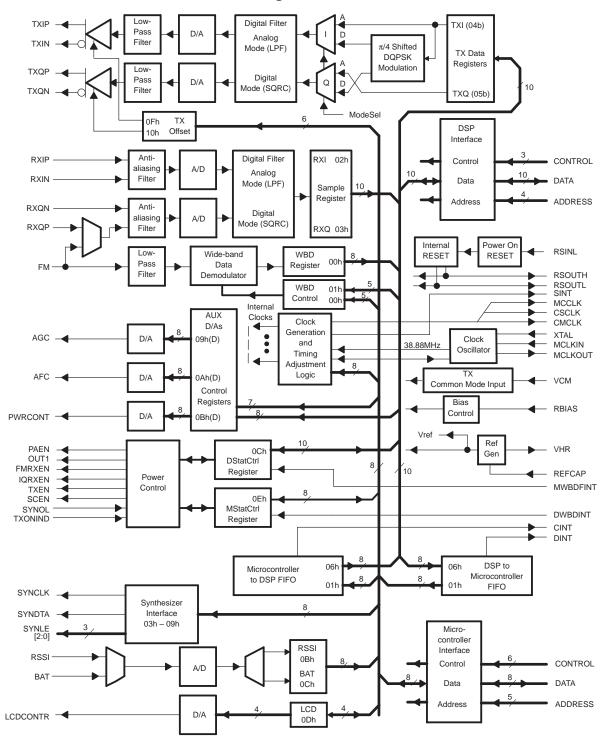

Texas Instruments (TI™) TCM4300 IS-54B advanced RF cellular telephone interface circuit (ARCTIC™) provides a baseband interface between the digital signal processor (DSP), the microcontroller, and the RF modulator/demodulator in a dual-mode IS-54B cellular telephone. See the *TCM4300 functional block diagram*.

In the analog mode, the TCM4300 provides all required baseband filtering as well as transmit D/A conversion and receive A/D conversion using dual 10-bit sigma-delta converters. In addition, a wide-band data (WBD) –10 kb/s Manchester frequency shift key (FSK) demodulator is provided to allow reduced DSP processing load during subscriber standby mode.

In the digital mode, the TCM4300 accepts I and Q baseband data and performs A/D and D/A conversion and square-root raised-cosine filtering using dual 10-bit sigma-delta converters. The TCM4300 also has a  $\pi$ /4-DQPSK modulation encoder for dibit-to-symbol conversion in the digital transmit mode.

The microcontroller interface is compatible with a wide range of microcontrollers. A microcontroller can be used to communicate with the user interface (keyboard, display, etc.) and to program up to three frequency synthesizers by using the on-chip synthesizer interface circuit.

The TCM4300 provides advanced power control to minimize the power consumption of many dual-mode telephone functional blocks such as the speech codec, FM receiver, I and Q demodulator, transmitter signal processor, and RF power amplifier. In addition, the TCM4300 is designed to reduce system power consumption through low-voltage operation and standby mode.

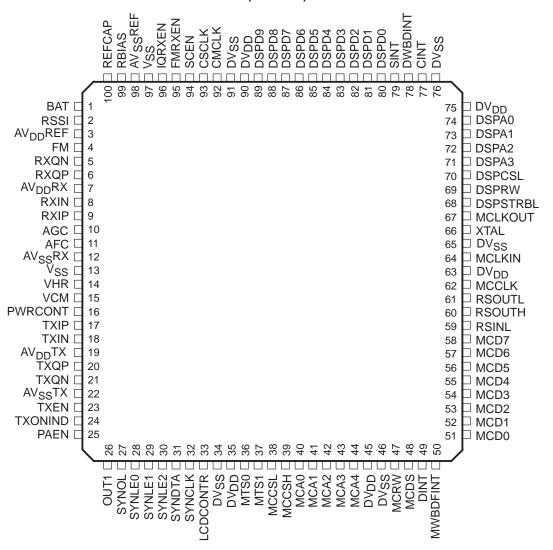

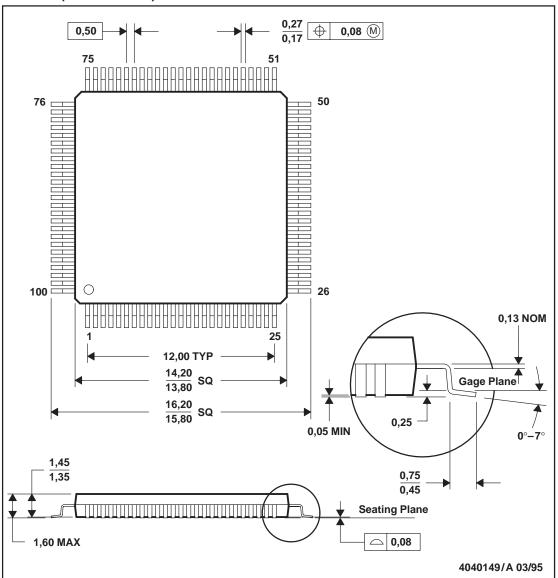

The TCM4300 is offered in the 100-pin PZ package and is characterized for free-air operation from -40°C to 85°C.

#### 1.1 Features

- Compliance With TIA IS-54B Dual-Mode Cellular Standard

- Baseband Transmit Digital-to-Analog (D/A) Conversion and Receive Analog-to-Digital (A/D) Conversion in Analog Transmit Mode Using Dual 10-Bit Sigma-Delta Converters

- Square Root Raised Cosine (SQRC) Filtering in the Digital Mode Using Dual 10-Bit Sigma-Delta Converters

- π/4-Differential Quadrature Phase-Shift Key (DQPSK) Modulation Encoder in Digital Transmit Mode

- Power Control Supervision for Radio Frequency (RF) Power Amplifier, Automatic Frequency Control (AFC), Automatic Gain Control (AGC), and Synthesizer

- Received Signal Strength Indicator (RSSI) and Battery-Level A/D Conversion Circuitry

- Internal Clock Generation

- WBD Clock Recovery and Manchester Decoding

- General-Purpose DSP and Microcontroller Interface

- 3.3-V and 5-V Operation

- Low Power Consumption

TI and ARCTIC are trademarks of Texas Instruments Incorporated.

### 1.2 TCM4300 Functional Block Diagram

### 1.3 Pin Assignments

### 1.4 Terminal Functions

| TERMINAL             |     |       |                                                                                                                                                                                                         |  |  |  |

|----------------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                 | NO. | 1/0   | DESCRIPTION                                                                                                                                                                                             |  |  |  |

| AFC                  | 11  | 0     | Automatic frequency control. The AFC DAC output provides the means to adjust system temperature-compensated reference oscillator (TCXO).                                                                |  |  |  |

| AGC                  | 10  | 0     | Automatic gain control. The AGC digital-to-analog converter (DAC) output can bused to control the gain of system receiver circuits.                                                                     |  |  |  |

| AV <sub>DD</sub> REF | 3   | _     | Analog supply voltage for FM receive path. Power applied to $AV_{\mbox{DD}}REF$ powers the FM receive path circuitry.                                                                                   |  |  |  |

| AV <sub>DD</sub> RX  | 7   | _     | Analog supply voltage for receive path. Power applied to AV <sub>DD</sub> RX powers the receive path circuitry.                                                                                         |  |  |  |

| AV <sub>DD</sub> TX  | 19  | _     | Analog supply voltage for transmit path. Power applied to AVDDTX powers the transmit path circuitry.                                                                                                    |  |  |  |

| AV <sub>SS</sub> REF | 98  | _     | Analog ground for REFCAP                                                                                                                                                                                |  |  |  |

| AVSSRX               | 12  | _     | Analog ground for receive path                                                                                                                                                                          |  |  |  |

| AV <sub>SS</sub> TX  | 22  |       | Analog ground for transmit path                                                                                                                                                                         |  |  |  |

| BAT                  | 1   | I     | Battery strength monitor. A sample of the battery voltage is applied to BAT, and this sample monitors the battery strength.                                                                             |  |  |  |

| CINT                 | 77  | 0     | Controller data interrupt. CINT is the microcontroller data interrupt (active low) signal that is sent to the DSP. CINT is caused by a microcontroller write to the Send-C interrupt register location. |  |  |  |

| CMCLK                | 92  | 0     | Codec master clock. CMCLK provides a 2.048-MHz clock that is used as the master clock and bit clock for the speech codec.                                                                               |  |  |  |

| CSCLK                | 93  | 0     | Codec sample clock. CSCLK provides an 8-kHz frame synchronization pulse for the speech codec. CSCLK is also connected to the DSP for speech sample interrupts.                                          |  |  |  |

| DINT                 | 49  | 0     | Microcontroller interrupt request. DINT is output when the DSP writes to the SEND DINT register location. DINT can be active high or low according to the levels of the MTS0 and MTS1 signals.          |  |  |  |

| DSPA0                | 74  | Ι     | DSP 4-bit parallel address bus. DSPA0 through DSPA3 provides the address bus for                                                                                                                        |  |  |  |

| DSPA1                | 73  |       | the DSP interface. DSPA3 is the MSB, and DSPA0 is the LSB.                                                                                                                                              |  |  |  |

| DSPA2                | 72  |       |                                                                                                                                                                                                         |  |  |  |

| DSPA3                | 71  |       |                                                                                                                                                                                                         |  |  |  |

| DSPCSL               | 70  | I     | DSP chip select (active low). A low signal at DSPCSL enables the specific DSP addressed.                                                                                                                |  |  |  |

| DSPD0                | 80  | I/O/Z | DSP 10-bit parallel data bus. DSPD0 through DSPD9 provide a 10-bit data bus for the                                                                                                                     |  |  |  |

| DSPD1                | 81  |       | DSP. DSPD9 is the MSB, and DSPD0 is the LSB.                                                                                                                                                            |  |  |  |

| DSPD2                | 82  |       |                                                                                                                                                                                                         |  |  |  |

| DSPD3                | 83  |       |                                                                                                                                                                                                         |  |  |  |

| DSPD4                | 84  |       |                                                                                                                                                                                                         |  |  |  |

| DSPD5                | 85  |       |                                                                                                                                                                                                         |  |  |  |

| DSPD6                | 86  |       |                                                                                                                                                                                                         |  |  |  |

| DSPD7                | 87  |       |                                                                                                                                                                                                         |  |  |  |

| DSPD8                | 88  |       |                                                                                                                                                                                                         |  |  |  |

| DSPD9                | 89  |       |                                                                                                                                                                                                         |  |  |  |

$<sup>\</sup>dagger Z = high impedance$

## 1.4 Terminal Functions (Continued)

| TERMINAL         |                       |       |                                                                                                                                                                |  |  |  |

|------------------|-----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME             | NO.                   | 1/0   | DESCRIPTION                                                                                                                                                    |  |  |  |

| DSPRW            | 69                    | I     | DSP read/write. A high on DSPRW enables a read operation and a low enables a write operation to the DSP.                                                       |  |  |  |

| DSPSTRBL         | 68                    | I     | DSP strobe low. The DSPSTRL (active low) is used in conjunction with DSP to enable read/write operations to the DSP.                                           |  |  |  |

| DV <sub>DD</sub> | 35, 45, 63,<br>75, 90 | _     | Digital power supply. All supply terminals must be connected together.                                                                                         |  |  |  |

| DV <sub>SS</sub> | 34, 46, 65,<br>76, 91 | _     | Digital ground. All supply terminals must be connected together.                                                                                               |  |  |  |

| DWBDINT          | 78                    | 0     | DSP wide-band data interrupt (active low). The DWBDINT output goes low to indicate that the WBD demodulation circuits have traffic on them.                    |  |  |  |

| FM               | 4                     | I     | Frequency modulation. FM terminal is connected to the output of the FM discriminator.                                                                          |  |  |  |

| FMRXEN           | 95                    | 0     | FM receive path enable. A high output from FMRXEN can be used to enable the power for the receiver FM path.                                                    |  |  |  |

| IQRXEN           | 96                    | 0     | In-phase and quadrature receive path enable. A high output on IQRXEN can be used to enable the power for receiver I/Q path.                                    |  |  |  |

| LCDCONTR         | 33                    | 0     | Liquid-crystal display (LCD) contrast. This LCDCONTR control DAC can be used to control the amount of drive to the liquid crystal display.                     |  |  |  |

| MCLKOUT          | 67                    | 0     | Master clock out. MCLKOUT is a buffered version of MCLKIN.                                                                                                     |  |  |  |

| MCA0             | 40                    | ı     | Microcontroller 5-bit parallel address bus. MCA0 through MCA4 provide a 5-bit                                                                                  |  |  |  |

| MCA1             | 41                    |       | bus to address the microcontroller. MCA4 is the MSB, and MCA0 is the LSB.                                                                                      |  |  |  |

| MCA2             | 42                    |       |                                                                                                                                                                |  |  |  |

| MCA3             | 43                    |       |                                                                                                                                                                |  |  |  |

| MCA4             | 44                    |       |                                                                                                                                                                |  |  |  |

| MCCLK            | 62                    | 0     | Microcontroller clock. MCCLK provides an adjustable frequency with 1.215 MHz at powerup.                                                                       |  |  |  |

| MCCSH            | 39                    | I     | Microcontroller interface chip-select. A high at MCCSH in conjunction with a low at MCCSL allows the microcontroller to read from or write to the TCM4300.     |  |  |  |

| MCCSL            | 38                    | I     | Microcontroller interface chip-select. A low at MCCSL in conjunction with a high at the MCCSH allows the microcontroller to read from or write to the TCM4300. |  |  |  |

| MCD0             | 51                    | I/O/Z | Microcontroller 8-bit parallel data bus. MCD0 through MCD7 provides an 8-bit                                                                                   |  |  |  |

| MCD1             | 52                    |       | parallel data bus to send/receive data to/from the microcontroller. MCD7 is the                                                                                |  |  |  |

| MCD2             | 53                    |       | MSB, and MCD0 is the LSB.                                                                                                                                      |  |  |  |

| MCD3             | 54                    |       |                                                                                                                                                                |  |  |  |

| MCD4             | 55                    |       |                                                                                                                                                                |  |  |  |

| MCD5             | 56                    |       |                                                                                                                                                                |  |  |  |

| MCD6             | 57                    |       |                                                                                                                                                                |  |  |  |

| MCD7             | 58                    |       |                                                                                                                                                                |  |  |  |

$<sup>\</sup>dagger Z = \text{high impedance}$

### 1.4 Terminal Functions (Continued)

| TERMINAL |     |     | DECORIDATION                                                                                                                                                                                                                                                                                            |  |  |  |

|----------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                             |  |  |  |

| MCDS     | 48  | I   | Microcontroller data strobe. MCDS is configured by the signals present on MTS0 and MTS1.                                                                                                                                                                                                                |  |  |  |

| MCLKIN   | 64  | I   | Master clock input. The MCLKIN frequency input requirement is $38.88\text{MHz}\pm100\text{ppm}$ . A crystal can be connected between MCLKIN and XTAL to provide an oscillator circuit. As an alternative, XTAL can be left open and an external TTL/CMOS-level clock signal can be connected to MCLKIN. |  |  |  |

| MCRW     | 47  | I   | Microcontroller read/write. Microcontroller read/write operations are selected in accordance with the signals present on MTS0 and MTS1.                                                                                                                                                                 |  |  |  |

| MTS0     | 36  | ı   | Microcontroller type select configuration-control inputs. The interface is controlled by MTS (1:0) as follows:  00 – Intel™ microcontroller interface characteristics                                                                                                                                   |  |  |  |

| MTS1     | 37  | ı   | 10 – Mitsubishi™ and Motorola™ microcontroller 16-bit bus interface characteristics<br>01 – Motorola™ microcontroller 8-bit bus characteristics<br>11 – Reserved                                                                                                                                        |  |  |  |

| MWBDFINT | 50  | 0   | Microcontroller interrupt request. A wide-band data-ready interrupt is output when the WBD demodulator is in analog mode or when a frame interrupt is sent by the DSP in digital mode. MWDBFINT can be active high or low according to the levels of the MTS0 and MTS1 signals.                         |  |  |  |

| OUT1     | 26  | 0   | Output number 1. OUT1 provides a user-defined general purpose data or control signal.                                                                                                                                                                                                                   |  |  |  |

| PAEN     | 25  | 0   | Power amplifier enable. PAEN can be used to enable the transmit power amplifier. This signal is active high.                                                                                                                                                                                            |  |  |  |

| PWRCONT  | 16  | 0   | Power amplifier (PA) power control. The PWRCONT DAC output can be used to control the amount of power output from the PA.                                                                                                                                                                               |  |  |  |

| RBIAS    | 99  | I   | Input for bias current-setting resistor. To achieve correct bias voltage, a 100-k $\Omega$ , 1% tolerance resistor connected between RBIAS and AVSS is recommended.                                                                                                                                     |  |  |  |

| REFCAP   | 100 | ı   | Reference decoupling capacitor. For proper decoupling, It is recommended that a $3.3\mu\text{F}$ capacitor in parallel with a 470-pF capacitor be connected between REFCAP and ground.                                                                                                                  |  |  |  |

| RSINL    | 59  | Ι   | Reset input low. An active low applied to RSINL resets the TCM4300.                                                                                                                                                                                                                                     |  |  |  |

| RSSI     | 2   | ı   | Received signal strength indicator. RSSI samples received signal strength.                                                                                                                                                                                                                              |  |  |  |

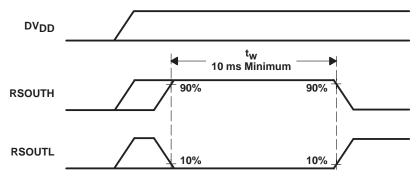

| RSOUTH   | 60  | 0   | Reset out high. An active high is output from RSOUTH for 10 ms after the TCM4300 is powered up.                                                                                                                                                                                                         |  |  |  |

| RSOUTL   | 61  | 0   | Reset out low. An active low is output from RSOUTL for 10 ms after the TCM4300 is powered up.                                                                                                                                                                                                           |  |  |  |

| RXIN     | 8   | I   | Negative receive input. The in-phase differential negative baseband received signal is applied to RXIN.                                                                                                                                                                                                 |  |  |  |

| RXIP     | 9   | ı   | Positive receive input. The in-phase differential positive baseband received signal is applied to RXIP.                                                                                                                                                                                                 |  |  |  |

| RXQN     | 5   | I   | Negative receive input. The quadrature negative baseband received signal is applied to RXQN.                                                                                                                                                                                                            |  |  |  |

| RXQP     | 6   | I   | Positive receive input. The quadrature differential positive baseband received signal is applied to RXQP.                                                                                                                                                                                               |  |  |  |

Intel is a trademark of Intel Corporation. Mitsubishi is a trademark of Mitsubishi Inc. Motorola is a trademark of Motorola, Inc.

## 1.4 Terminal Functions (Continued)

| TERMI    | NAL    | .,, |                                                                                                                                                |  |  |  |

|----------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | NO.    | 1/0 | DESCRIPTION                                                                                                                                    |  |  |  |

| SCEN     | 94     | 0   | Speech CODEC enable. A high out from SCEN can enable the speech CODEC.                                                                         |  |  |  |

| SINT     | 79     | 0   | Sample interrupt. SINT is active low. In the analog mode, SINT occurs at 40 kHz; in the digital mode, SINT occurs at 48.6 kHz.                 |  |  |  |

| SYNCLK   | 32     | 0   | Synthesizer clock. SYNCLK clocks the serial data stream.                                                                                       |  |  |  |

| SYNDTA   | 31     | 0   | Synthesizer serial-data. SYNDTA provides the serial bit stream output.                                                                         |  |  |  |

| SYNLE0   | 28     | 0   | Synthesizer 0, 1, and 2 latch enables. An active high on SYNLE0, SYNLE1, and                                                                   |  |  |  |

| SYNLE1   | 29     | 0   | SYNLE2 indicates that the latch is enabled.                                                                                                    |  |  |  |

| SYNLE2   | 30     | 0   |                                                                                                                                                |  |  |  |

| SYNOL    | 27     | I   | Synthesizer out-of-lock. An active high at SYNOL indicates a synthesizer is not locked.                                                        |  |  |  |

| TXEN     | 23     | 0   | Transmit power enable. An active high output from TXEN can be used to enable various system transmitter-circuit devices.                       |  |  |  |

| TXIN     | 18     | 0   | In-phase differential negative baseband transmit. The negative component of the differential baseband transmit signal is output from TXIN.     |  |  |  |

| TXIP     | 17     | 0   | In-phase differential positive baseband transmit. The positive component differential baseband transmit signal is output from TXIP.            |  |  |  |

| TXONIND  | 24     | I   | Transmit on indicator. A signal is applied to TXONIND to indicate that power is applied to the power amplifier.                                |  |  |  |

| TXQN     | 21     | 0   | Quadrature differential negative baseband transmit. The negative component of the quadrature differential transmit signal is output from TXQN. |  |  |  |

| TXQP     | 20     | 0   | Quadrature differential positive baseband transmit. The positive component of the quadrature differential transmit signal is output from TXQP. |  |  |  |

| VCM      | 15     | I   | Voltage common mode. VCM establishes the dc operating point for transmit outputs and can be tied to VHR.                                       |  |  |  |

| VHR 14 O |        | 0   | Voltage half-rail. The voltage level at VHR is approximately 0.5 $\times$ AVDD. VHR establishes the dc operating point for receive inputs.     |  |  |  |

| VSS      | 13, 97 | _   | Substrate ground                                                                                                                               |  |  |  |

| XTAL     | 66     | Ι   | Crystal input. A crystal connected between XTAL and MCLIN forms an oscillator circuit.                                                         |  |  |  |

### 2 Electrical Specifications

This section lists the electrical specifications, the absolute maximum ratings, the recommended operating conditions and operating characteristics for the TCM4300 Advanced RF Cellular Telephone Interface Circuit.

## 2.1 Absolute Maximum Ratings Over Operating Free-Air Temperature Range (unless otherwise noted)<sup>†</sup>

| Supply voltage range:                                                           |                      |

|---------------------------------------------------------------------------------|----------------------|

| $DV_{DD}$ (see Notes 1 and 2) $V_{SS}$ –0.3 V to $AV_{D}$                       | <sub>DD</sub> +0.3 V |

| AV <sub>DD</sub> (see Notes 2 and 3) V <sub>SS</sub> -0.3 V to DV <sub>E</sub>  | <sub>DD</sub> +0.3 V |

| Input voltage range, $V_I$ : Digital signals $V_{SS} - 0.3 \text{ V to DV}_{I}$ | <sub>DD</sub> +0.3 V |

| Analog signals V <sub>SS</sub> –0.3 V to AV <sub>E</sub>                        | <sub>DD</sub> +0.3 V |

| Output voltage range, V <sub>O</sub> : Digital signals V <sub>SS</sub>          | to DV <sub>DD</sub>  |

| Analog signals V <sub>SS</sub>                                                  | to AV <sub>DD</sub>  |

| Continuous total power dissipation See Dissipation Rate                         | ting Table           |

| Operating free-air temperature range, T <sub>A</sub>                            | C to 85°C            |

| Storage temperature range, T <sub>Stg</sub> –65°C                               | to 150°C             |

| Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds                    | 260°C                |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. Voltage values are with respect DVSS.

- 2. Maximum supplied voltage should not exceed 6 V.

- 3. Voltage values are with respect to AVSS.

#### 2.2 Dissipation Rating Table

| PACKAGE | $T_{\mbox{\scriptsize A}} \le 25^{\circ}\mbox{\scriptsize C}$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|----------------------------------------------------------------------------|------------------------------------------------|---------------------------------------|

| PZ      | 1530 mW                                                                    | 15.25 mW/°C                                    | 615 mW                                |

### 2.3 Recommended Operating Conditions

|                                                           |         | MIN                  | NOM | MAX                   | UNIT |

|-----------------------------------------------------------|---------|----------------------|-----|-----------------------|------|

| Supply voltage, DV <sub>DD</sub>                          |         | 3                    |     | 5.5                   | V    |

| High-level input voltage, VIH                             | Digital | 0.7 DV <sub>DD</sub> |     | DV <sub>DD</sub> +0.3 | V    |

| Low-level input voltage, V <sub>IL</sub>                  | Digital | 0                    |     | 0.3 DV <sub>DD</sub>  | V    |

| High-level output voltage, VOH                            | Digital | 0.7 DV <sub>DD</sub> |     | $DV_DD$               | V    |

| Low-level output voltage, VOL                             | Digital | 0                    |     | 0.5                   | V    |

| High-level output current at 3 V, IOH                     | Digital | 2                    |     |                       | mA   |

| Low-level output current at 3 V, IOL                      | Digital | 2                    |     |                       | mA   |

| High-level output current at 5 V, IOH                     | Digital | 2                    |     |                       | mA   |

| Low-level output current at 5 V, IOL                      | Digital | 2                    |     |                       | mA   |

| Load capacitance, transmit I and Q channel outputs        |         |                      | 50  |                       | pF   |

| VCM input voltage range, transmit I and Q channel outputs |         | 1.3                  |     | AV <sub>DD</sub> -1.3 | V    |

| Load resistance, auxiliary DACs                           |         | 10                   |     | kΩ                    |      |

| Load capacitance, auxiliary DACs                          |         | 50                   |     | pF                    |      |

| Operating free-air temperature, TA                        |         | -40                  |     | 85                    | °C   |

# 2.4 Electrical Characteristics Over Full Range Of Operating Conditions (Unless Otherwise Noted)

#### 2.4.1 Power Consumption

| PAR                   | AMETER                    | TEST CO                   | MIN                      | TYP† | MAX | UNIT |       |

|-----------------------|---------------------------|---------------------------|--------------------------|------|-----|------|-------|

| A note a transmitting | and receiving             | $DV_{DD} = 3 V$ ,         | $AV_{DD} = 3 V$          |      | 65  | 75   | mW    |

| Analog transmitting   | and receiving             | $DV_{DD} = 5.5 V,$        | $AV_{DD} = 5.5 V$        |      | 250 | 275  | IIIVV |

| Digital receiving     |                           | $DV_{DD} = 3 V$ ,         | $AV_{DD} = 3 V$          |      | 55  | 60   | m\//  |

| Digital receiving     |                           | $DV_{DD} = 5.5 V,$        | $AV_{DD} = 5.5 V$        |      | 225 | 250  | mW    |

| Digital transmitting  |                           | $DV_{DD} = 3 V$ ,         | $AV_{DD} = 3 V$          |      | 55  | 70   | mW    |

| Digital transmitting  |                           | $DV_{DD} = 5.5 V,$        | $AV_{DD} = 5.5 V$        |      | 210 | 250  | IIIVV |

|                       | MCLKOUT enabled           | $DV_{DD} = 3 V$ ,         | $AV_{DD} = 3 V$          |      | 33  | 40   |       |

| Idle mode             | MCLKOUT disabled          | $DV_{DD} = 3 V$ ,         | $AV_{DD} = 3 V$          |      | 14  | 17   | mW    |

| idle mode             | MCLKOUT enabled           | $DV_{DD} = 5.5 V,$        | AV <sub>DD</sub> = 5.5 V |      | 150 | 160  | 11100 |

|                       | MCLKOUT disabled          | $DV_{DD} = 5.5 V,$        | $AV_{DD} = 5.5 V$        |      | 80  | 90   |       |

| Digital mode, 1/3 tra | insmitting +1/3 receiving | $DV_{DD} = 3 V$ ,         | $AV_{DD} = 3 V$          |      | 50  | 60   | \A/   |

| + 1/3 standby         |                           | DV <sub>DD</sub> = 5.5 V, | AV <sub>DD</sub> = 5.5 V |      | 205 | 220  | mW    |

<sup>†</sup> All typical values are at T<sub>A</sub> = 25°C.

### 2.4.2 Reference Characteristics

| PARAMETER |                           | TEST CONDITIONS                | MIN                       | TYP <sup>†</sup> | MAX                       | UNIT |

|-----------|---------------------------|--------------------------------|---------------------------|------------------|---------------------------|------|

| VOH(VHR)  | High-level output voltage |                                | 0.5 AV <sub>DD</sub> -0.2 |                  | 0.5 AV <sub>DD</sub> +0.2 | V    |

| ro        | Output resistance         | FMVOX or IQRXEN or TXEN = high |                           | 80               | 100                       | Ω    |

|           |                           | FMVOX or IQRXEN or TXEN = low  | 15                        | 40               |                           | kΩ   |

<sup>†</sup> All typical values are at DV<sub>DD</sub> = 5 V,  $AV_{DD}$  = 5 V, and  $T_A$  = 25°C

### 2.4.3 Terminal Impedance

| FUNCTION                                                            |                  |    | TYP† | MAX | UNIT |

|---------------------------------------------------------------------|------------------|----|------|-----|------|

| Receive channel input impedance (single ended), RXIP/N and RXQP/N   |                  |    | 70   |     | kΩ   |

| Transmit channel output impedance (single ended), TXIP/N and TXQP/N |                  |    | 50   | 100 | Ω    |

| FM input impedance, WBD                                             |                  | 25 | 200  |     | kΩ   |

| MCLKOUT impedance                                                   | MCLKOUT at 3.3 V |    | 240  |     | Ω    |

| MCLKOUT impedance                                                   | MCLKOUT at 5 V   |    | 180  |     | 52   |

$<sup>\</sup>dagger$  All typical values are at DV<sub>DD</sub> = 5 V, AV<sub>DD</sub> = 5 V, and T<sub>A</sub> = 25°C, unless otherwise specified.

## 2.4.4 RXIP, RXIN, RXQP, and RXQN Inputs (AV<sub>DD</sub> = 3 V, 4.5 V, 5 V)

| PARAMETER                                           |                                                     | TEST CONDITIONS            | MIN | TYP   | MAX                   | UNIT  |

|-----------------------------------------------------|-----------------------------------------------------|----------------------------|-----|-------|-----------------------|-------|

| Input voltage range                                 |                                                     |                            | 0.3 |       | AV <sub>DD</sub> -0.3 | V     |

| Input voltage for full-                             | Differential                                        |                            |     | 0.5   |                       | Vn n  |

| scale digital output                                | Single ended                                        |                            |     | 0.5   |                       | Vp-p  |

| Nominal operating                                   | Differential                                        |                            |     | 0.125 |                       | Vp-p† |

| level                                               | Single ended                                        |                            |     | 0.125 |                       | νρ-ρ1 |

| Input CMRR (RXI, RXQ                                | )                                                   |                            | 45  |       |                       | dB    |

| Sampling frequency, SIN mode)                       | NT (digital                                         |                            |     | 48.6  |                       | kHz   |

| Sampling frequency, SIN mode)                       | NT (analog                                          |                            |     | 40    |                       | kHz   |

| Receive error vector ma                             | gnitude (EVM)                                       |                            |     | 5%    | 6%                    |       |

| I/Q sample timing skew                              |                                                     | Input signal 0 – 15 kHz    |     | 50    |                       | ns    |

| A/D resolution                                      |                                                     |                            |     | 10    |                       | bits  |

| Signal-to-noise plus dist                           | ortion                                              | Input at full scale – 1 dB | 54  | 58    |                       | dB    |

| Integral nonlinearity                               |                                                     | 0 dB to -60 dB input       |     | 1     |                       | LSB   |

| Gain error (I or Q chann                            | el)                                                 |                            |     |       | ±7%                   |       |

| Gain mismatch betweer                               | l and Q                                             |                            |     |       | ±0.3                  | dB    |

| Differential dc offset volt                         | age                                                 |                            |     |       | ±30                   | mV    |

| FM input sensitivity, full $(\pm$ 14-kHz deviation) | scale                                               |                            |     | 2.5   |                       | Vp-p  |

| FM input dc offset (relative to VHR)                |                                                     |                            |     |       | ±80                   | mV    |

| FM input idle channel no full-scale input           | FM input idle channel noise, below full-scale input |                            |     |       | -50                   | dB    |

| FM gain error                                       |                                                     |                            |     |       | ±6%                   |       |

| Power supply rejection                              |                                                     | f = 0 kHz to 15 kHz        |     | 40    |                       | dB    |

<sup>†</sup> Provides 12-dB headroom for AGC fading conditions.

### 2.4.5 Transmit I and Q Channel Outputs

| PARAMETER                                                            |                  |    | TYP  | MAX   | UNIT   |

|----------------------------------------------------------------------|------------------|----|------|-------|--------|

| Peak output voltage full coals, contered at VCM                      | Differential     |    | 2.24 |       | \/n    |

| Peak output voltage full scale, centered at VCM                      | Single ended     |    | 1.12 |       | Vp     |

| Nominal output-level (constellation radius) centered                 |                  |    | 1.5  |       | V      |

| at VCM                                                               | Single ended     |    | 0.75 |       | V      |

| Low-level drift                                                      |                  |    | ±200 |       | PPM/°C |

| Transmit error vector magnitude (EVM)                                |                  |    | 3%   | 4%    |        |

| Transmit DACs I and Q resolution                                     |                  |    | 8    |       | bits   |

| S/(N+D) ratio at differential outputs                                |                  | 48 | 52   |       | dB     |

| Gain error (I or Q channel)                                          |                  |    | ±8%  | ±12%  |        |

| Gain mismatch between I and Q                                        |                  |    |      | ±0.3  | dB     |

| Gain sampling mismatch between I and Q                               |                  |    | 20   |       | ns     |

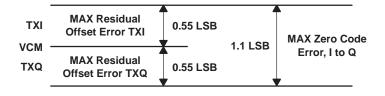

| Zero code error, I to Q, with respect to other channel single ended) | (differential or |    |      | ±1.1  | LSB    |

| Residual offset error, I or Q, with respect to VCM                   |                  |    |      | ±0.55 | LSB    |

| Load impedance, between P and N terminals                            |                  | 10 |      |       | kΩ     |

| Transmit offset DACs I and Q resolution                              |                  |    | 6    |       | bits   |

| Transmit offset DACs I and Q average step size                       |                  |    |      | 5.0   | mV     |

| Transmit offset DACs differential nonlinearity                       |                  |    |      | ±1.1  | LSB    |

| Transmit offset DACs integral nonlinearity                           |                  |    |      | ±1.1  | LSB    |

### 2.4.6 Auxiliary D/A Converters

| PARAMETER                                                 | TEST CO                                 | ONDITIONS        | MIN | TYP   | MAX | UNIT |

|-----------------------------------------------------------|-----------------------------------------|------------------|-----|-------|-----|------|

|                                                           | $AV_{DD} > 3 V^{\dagger}$               | AUXFS [1:0] = 00 | 0.2 |       | 2.5 |      |

| Output range                                              | AV <sub>DD</sub> > 4.5 V <sup>†</sup> , | AUXFS [1:0] = 10 | 0.2 |       | 4   | V    |

|                                                           | AV <sub>DD</sub> > 5 V <sup>†</sup> ,   | AUXFS [1:0] = 11 | 0.2 |       | 4.5 |      |

| Resolution AGC, AFC, PWRCONT DACs                         |                                         |                  |     | 8     |     | bits |

| Resolution LCDCONTR DAC                                   |                                         |                  |     | 4     |     | bits |

| Gain + offset error (full scale) AGC,<br>AFC, PWRCONT DAC |                                         |                  |     |       | ±3% |      |

| Gain + offset error (full scale)<br>LCDCONTR DAC          |                                         |                  |     |       | ±7% |      |

| Differential nonlinearity                                 |                                         |                  |     | ±0.75 | ±1  | LSB  |

| Integral nonlinearity                                     |                                         |                  |     | ±0.75 | ±1  | LSB  |

<sup>†</sup> Range settings depends only on AUXFS [1:0]. The supply voltage is not detected.

### 2.4.7 Auxiliary D/A Converters Slope (AGC, AFC, PWRCONT)

| AUXFS[1:0]<br>SETTING | SLOPE         | NOMINAL LSB<br>VALUE<br>(V) | NOMINAL OUTPUT VOLTAGE<br>FOR DIGITAL CODE = 128<br>(MIDRANGE)<br>(V) | NOMINAL OUTPUT VOLTAGE<br>FOR DIGITAL CODE = 256 <sup>†</sup><br>(MAX VALUE)<br>(V) |

|-----------------------|---------------|-----------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| 00                    | 2.5/256       | 0.0098                      | 1.25                                                                  | 2.5                                                                                 |

| 01                    | Do not<br>use | Do not use                  | Do not use                                                            | Do not use                                                                          |

| 10                    | 4/256         | 0.0156                      | 2                                                                     | 4                                                                                   |

| 11                    | 4.5/256       | 0.0176                      | 2.25                                                                  | 4.5                                                                                 |

<sup>†</sup> The maximum input code is 255. The value shown for 256 is extrapolated.

### 2.4.8 Auxiliary D/A Converters Slope (LCDCONTR)

| AUXFS[1:0]<br>SETTING | SLOPE      | NOMINAL LSB<br>VALUE<br>(V) | NOMINAL OUTPUT VOLT-<br>AGE FOR DIGITAL CODE = 8<br>(MIDRANGE)<br>(V) | NOMINAL OUTPUT VOLTAGE<br>FOR DIGITAL CODE = 16 <sup>†</sup><br>(MAX VALUE)<br>(V) |

|-----------------------|------------|-----------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 00                    | 2.5/16     | 0.1563                      | 1.25                                                                  | 2.5                                                                                |

| 01                    | Do not use | Do not use                  | Do not use                                                            | Do not use                                                                         |

| 10                    | 4/16       | 0.2500                      | 2                                                                     | 4                                                                                  |

| 11                    | 4.5/16     | 0.2813                      | 2.25                                                                  | 4.5                                                                                |

<sup>†</sup> The maximum input code is 15. The value shown for 16 is extrapolated.

### 2.4.9 RSSI/Battery A/D Converter

| PARAMETER                        | TEST CONDITIONS                    | MIN | TYP   | MAX | UNIT |

|----------------------------------|------------------------------------|-----|-------|-----|------|

| Input range                      | AV <sub>DD</sub> = 3 V, 4.5 V, 5 V | 0.2 |       | 2   | V    |

| Resolution                       |                                    |     | 8     |     | bits |

| Conversion time                  | AV <sub>DD</sub> = 3 V, 4.5 V, 5 V |     | 20    |     | μs   |

| Gain + offset error (full scale) |                                    |     | ±3%   | ±4% |      |

| Differential nonlinearity        |                                    |     | ±0.75 | ±1  | LSB  |

| Integral nonlinearity            |                                    |     | ±0.75 | ±1  | LSB  |

| Input resistance                 |                                    | 1   | 2     |     | МΩ   |

## 2.5 Operating Characteristics Over Full Range of Operating Conditions (Unless Otherwise Noted)

### 2.5.1 Receive (RX) Channel Frequency Response (RXI, RXQ Input in Digital Mode)

|                                                  | . ,                   |                                 |     |      |       |      |

|--------------------------------------------------|-----------------------|---------------------------------|-----|------|-------|------|

| PARAMETER                                        | TEST                  | CONDITIONS                      | MIN | TYP  | MAX   | UNIT |

| Frequency                                        | 0.125 V peak-to-peak, | 0 kHz to 8 kHz (see Note 4)     |     | ±0.5 | ±0.75 |      |

|                                                  | 0.125 V peak-to-peak, | 8 kHz to 15 kHz (see Note 5)    |     |      | ±1    |      |

|                                                  | 0.125 V peak-to-peak, | 16.2 kHz to 18 kHz (see Note 5) |     |      | -26   | 40   |

| response                                         | 0.125 V peak-to-peak, | 18 kHz to 45 kHz (see Note 5)   |     |      | -30   | dB   |

|                                                  | 0.125 V peak-to-peak, | 45 kHz to 75 kHz (see Note 5)   |     |      | -46   |      |

|                                                  | 0.125 V peak-to-peak, | > 75 kHz                        |     |      | -60   |      |

| Peak-to-peak<br>group delay<br>distortion        | 0.125 V peak-to-peak, | 0 kHz to 15 kHz                 |     |      | 2     | μs   |

| Absolute channel delay, RXI, Q IN to digital OUT | 0.125 V peak-to-peak, | 0 kHz to 15 kHz                 |     | 325  |       | μs   |

NOTES: 4. Deviation from ideal 0.35 square-root raised-cosine (SQRC) response

5. Stopband

### 2.5.2 Receive (RX) Channel Frequency Response (FM Input in Analog Mode)

| PARAMETER                           | TEST CONDITIONS     |                               |  | TYP | MAX  | UNIT |

|-------------------------------------|---------------------|-------------------------------|--|-----|------|------|

|                                     | 2.5 V peak-to-peak, | 0 kHz to 6 kHz (see Note 6)   |  |     | ±0.5 |      |

| Frequency response                  | 2.5 V peak-to-peak, | 20 kHz to 30 kHz (see Note 5) |  |     | -18  | dB   |

|                                     | 2.5 V peak-to-peak, | 34 kHz to 46 kHz (see Note 7) |  |     | -48  |      |

| Peak-to-peak group delay distortion | 2.5 V peak-to-peak, | 0 kHz to 6 kHz                |  |     | 2    | μs   |

| Absolute channel delay              | 2.5 V peak-to-peak, | 0 kHz to 6 kHz                |  | 400 |      | μs   |

NOTES: 5. Stopband

6. Ripple magnitude

7. Stopband and multiples of stopband

#### 2.5.3 Transmit (TX) Channel Frequency Response (Digital Mode)

| PARAMETER                           | TEST CONDITIONS                                   |  | TYP | MAX  | UNIT |

|-------------------------------------|---------------------------------------------------|--|-----|------|------|

|                                     | 0 kHz to 8 kHz (see Note 4)                       |  |     | ±0.3 |      |

|                                     | 8 kHz to 15 kHz (see Note 4)                      |  |     | ±0.5 |      |

| F                                   | 20 kHz to 45 kHz (see Note 5)                     |  |     | -29  | 40   |

| Frequency response                  | 45 kHz to 75 kHz (see Note 5)                     |  |     | -55  | dB   |

|                                     | > 75 kHz (see Note 5)                             |  |     | -60  |      |

|                                     | Any 30 kHz band centered at > 90 kHz (see Note 5) |  |     | -60  |      |

| Peak-to-peak group delay distortion | 0 kHz to 15 kHz                                   |  |     | 3    | μs   |

| Absolute channel delay              | 0 kHz to 15 kHz                                   |  | 320 |      | μs   |

NOTES: 4. Deviation from ideal 0.35 square-root raised-cosine (SQRC) response

5. Stopband

#### Transmit (TX) Channel Frequency Response (Analog Mode) 2.5.4

| PARAMETER                           | TEST CONDITIONS                                   |  | TYP | MAX  | UNIT |

|-------------------------------------|---------------------------------------------------|--|-----|------|------|

| Frequency response                  | 0 kHz to 8 kHz (see Note 4)                       |  |     | ±0.5 |      |

|                                     | 8 kHz to 15 kHz (see Note 4)                      |  |     | ±0.5 |      |

|                                     | 20 kHz to 45 kHz (see Note 5)                     |  |     | -31  | dB   |

|                                     | 45 kHz to 75 kHz (see Note 5)                     |  |     | -70  | uБ   |

|                                     | > 75 kHz (see Note 5)                             |  |     | -70  |      |

|                                     | Any 30 kHz band centered at > 90 kHz (see Note 5) |  |     | -70  |      |

| Peak-to-peak group delay distortion | 0 kHz to 15 kHz                                   |  |     | 3    | μs   |

| Absolute channel delay              | 0 kHz to 15 kHz                                   |  | 540 |      | μs   |

NOTES: 4. Ripple magnitude 5. Stopband

#### 3 Parameter Measurement Information

This section contains the timing waveforms and parameter values for MCLKOUT and several microcontroller interface configurations possible when using the TCM4300. The timing parameters are contained in Section 3.1 through Section 3.11. The timing waveforms are shown in Figures 3–1 through 3–11. All parameters shown in the separate waveforms have their values listed in an associated table. Not all parameter values listed in the tables are necessarily shown in an associated waveform.

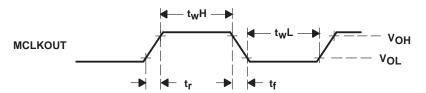

### 3.1 MCLKOUT Timing Requirements (see Figure 3–1 and Note 1)

|                 |                               | MIN | NOM | MAX | UNIT |

|-----------------|-------------------------------|-----|-----|-----|------|

| t <sub>wH</sub> | Pulse duration , MCLKOUT high | 9   | 10  | 12  | ns   |

| t <sub>wL</sub> | Pulse duration, MCLKOUT low   | 9   | 10  | 12  | ns   |

| t <sub>r</sub>  | Rise time, MCLKOUT            | 2   | 3   | 4   | ns   |

| tf              | Fall time, MCLKOUT            | 2   | 3   | 4   | ns   |

NOTE 1: Tested with 15 pF loading on MCLKOUT

Figure 3-1. MCLKOUT Timing Diagram

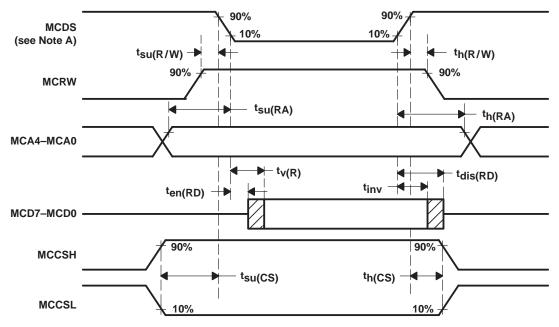

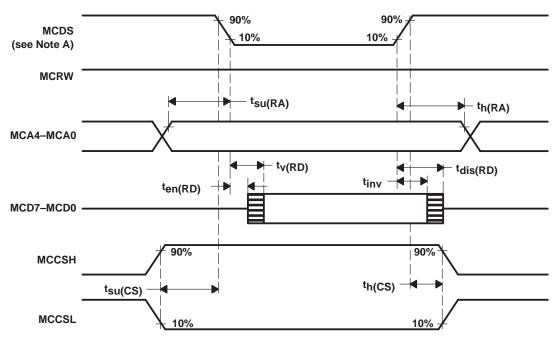

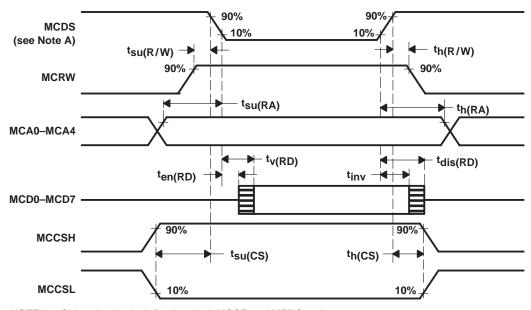

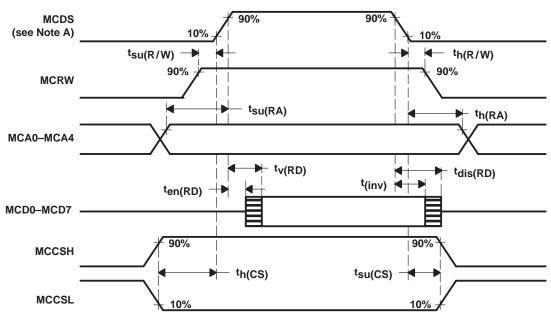

# 3.2 TCM4300 to Microcontroller Interface Timing Requirements (Mitsubishi Read Cycle) (see Figure 3–2 and Note 2)

|                      | PARAMETER                                                                               | ALTERNATE<br>SYMBOL  | MIN | MAX | UNIT |

|----------------------|-----------------------------------------------------------------------------------------|----------------------|-----|-----|------|

| t <sub>su(R/W)</sub> | Setup time, read/write MCRW stable before falling edge of strobe MCDS                   | TRW(SU)              | 0   |     | ns   |

| th(R/W)              | Hold time, read/write MCRW stable after rising edge of strobe MCDS                      | TRW(HO)              | 10  |     | ns   |

| t <sub>su(RA)</sub>  | Setup time, read address MCS stable before falling edge of strobe MCDS                  | TRA(SU)              | 0   |     | ns   |

| th(RA)               | Hold time, read address MCA stable after rising edge of strobe MCDS                     | TRA(HO)              | 10  |     | ns   |

| ten(RD)              | Enable time, read data on falling edge of strobe MCDS to TCM4300 driving data bus MCD   | TRD(EN)              | 10  |     | ns   |

| t <sub>V</sub> (R)   | Valid time read data on falling edge of strobe MCDS to valid data MCD                   | TRD <sub>(DV)</sub>  |     | 50  | ns   |

| t <sub>(inv)</sub>   | Data MCD invalid after rising edge of strobe MCDS                                       | TRD <sub>(INV)</sub> |     | 10  | ns   |

| tdis(RD)             | Disable time, read data. TCM4300 releases MCD data bus after rising edge of strobe MCDS | TRD(DIS)             |     | 28  | ns   |

| th(CS)               | Hold time, chip select MCCSH and MCCSL stable before rising edge of strobe MCDS         | TCS <sub>(HO)</sub>  | 0   |     | ns   |

| tsu(CS)              | Setup time, chip select MCCSH and MCCSL stable before falling edge of strobe MCDS       | TCS <sub>(SU)</sub>  | 0   |     | ns   |

NOTE 2: Timings are based upon Mitsubishi 37732S4 (16 MHz) and Mitsubishi 3772S4L (8 MHz).

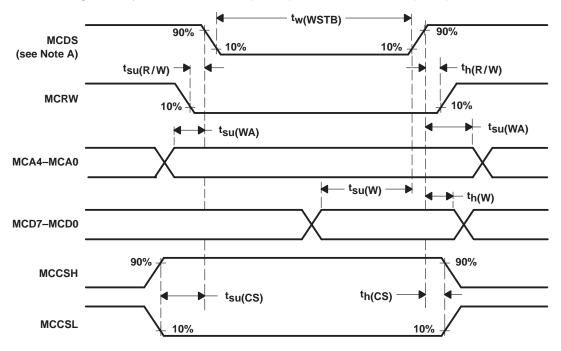

NOTE A: Chip selection is defined as both MCCS and MCDS active.

Figure 3–2. Microcontroller Interface Timing Requirements (Mitsubishi Configuration Read Cycle, MTS [1:0] = 10)

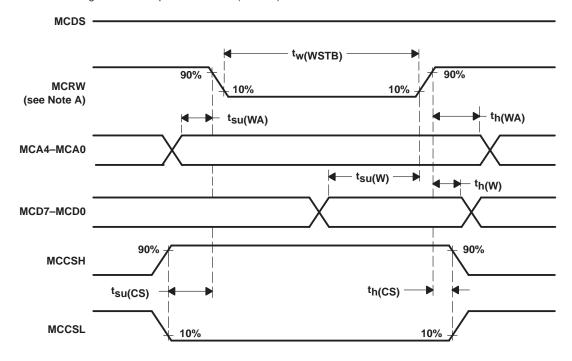

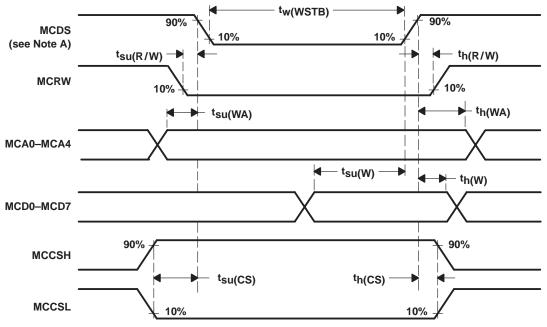

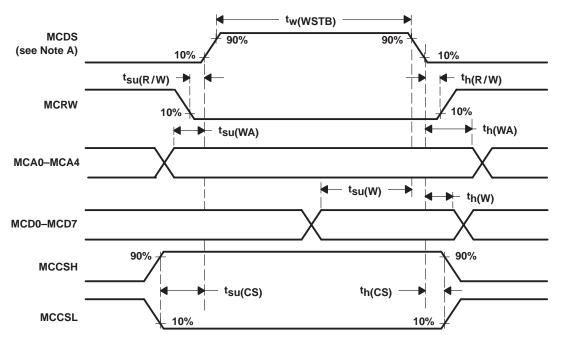

## 3.3 TCM4300 to Microcontroller Interface Timing Requirements (Mitsubishi Write Cycle) (see Figure 3–3 and Note 2)

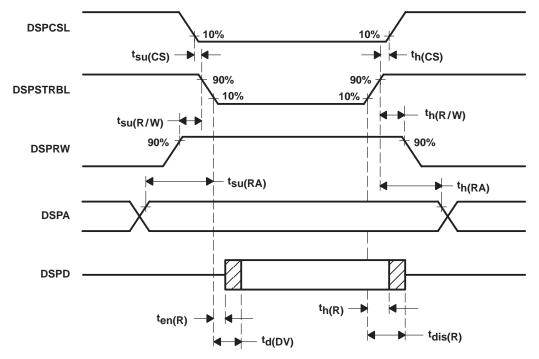

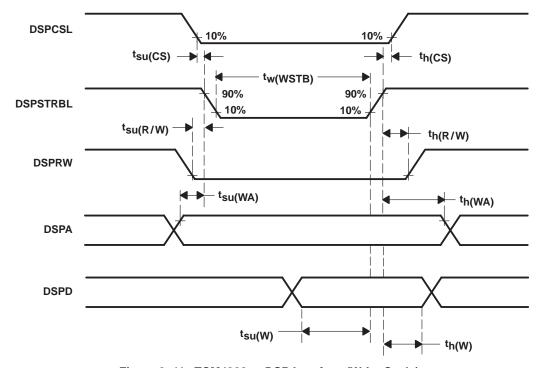

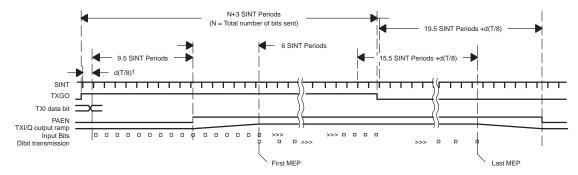

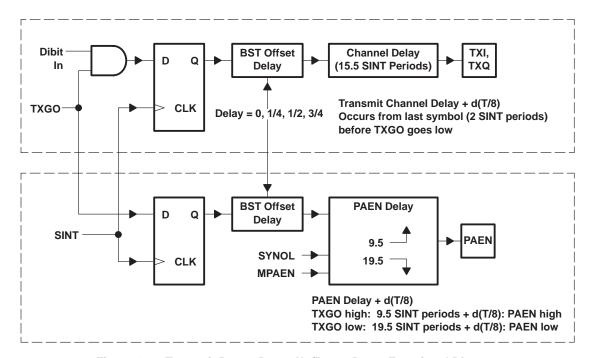

|                      | PARAMETER                                                                         | ALTERNATE<br>SYMBOL | MIN MAX | UNIT |