# MI.20xx

fast 8 bit transient recorder,

A/D converter board

for PCI bus

Hardware Manual Software Driver Manual

English version

April 1, 2005

# (c) SPECTRUM SYSTEMENTWICKLUNG MICROELECTRONIC GMBH AHRENSFELDER WEG 13-17, 22927 GROSSHANSDORF, GERMANY

SBench is a registered trademark of Spectrum Systementwicklung Microelectronic GmbH.

Microsoft, Visual C++, Visual Basic, Windows, Windows 98, Windows NT, Window 2000 and Windows XP are tradenarks/registered trademarks of Microsoft Corporation.

LabVIEW, DASYLab, Diadem and LabWindows/CVI are tradenarks/registered trademarks of National Instruments Corporation.

$\ensuremath{\mathsf{MATLAB}}$  is a tradenark/registered trademark of The Mathworks, Inc.

Agilent VEE, VEE Pro and VEE OneLab are tradenarks/registered trademarks of Agilent Technologies, Inc.

FlexPro is a registered trademark of Weisang GmbH & Co. KG.

| Introduction                                       | 6  |

|----------------------------------------------------|----|

| Preface                                            |    |

| General Information                                |    |

| Different models of the MI.20xx series             |    |

| Additional options                                 |    |

| Extra I/O (Option -XMF)                            |    |

| Extra I/O (Option -XIO)                            |    |

| Starhub                                            |    |

| Timestamp                                          |    |

| The Spectrum type plate                            |    |

| Hardware information.                              |    |

| Block diagram                                      |    |

| Technical Data                                     |    |

| Dynamic Parameters                                 |    |

| Order information.                                 |    |

|                                                    |    |

| Hardware Installation                              |    |

| System Requirements                                |    |

| Warnings                                           |    |

| ESD Precautions                                    | 13 |

| Cooling Precautions                                |    |

| Sources of noise                                   |    |

| Installing the board in the system                 |    |

| Installing a single board without any options      |    |

| Installing a board with digital inputs/outputs     |    |

| Installing a board with extra I/O (Option -XMF)    |    |

| Installing multiple boards synchronized by starhub |    |

| Installing multiple synchronized boards            |    |

| - ' '                                              |    |

| Software Driver Installation                       |    |

| Interrupt Sharing                                  |    |

| Windows 98                                         |    |

| Installation                                       |    |

| Version control                                    |    |

| Driver - Update                                    |    |

| Windows 2000                                       |    |

| Installation                                       |    |

| Version control                                    |    |

| Driver - Update                                    |    |

| Windows XP                                         |    |

| Installation                                       |    |

| Version control                                    |    |

| Driver - Update                                    |    |

| Windows NT                                         |    |

| Installation                                       | 24 |

| Adding boards to the Windows NT driver             | 24 |

| Driver - Update                                    |    |

| Linux                                              |    |

| Overview                                           |    |

| Installation                                       |    |

| oftware                                            | 27 |

|                                                    |    |

| Software Overview                                  |    |

| First Test with SBench                             |    |

| C/C++ Driver Interface                             |    |

| Header files                                       |    |

| Microsoft Visual C++                               |    |

| Linux Gnu C                                        |    |

| Other Windows C/C++ compilers                      |    |

| National Instruments LabWindows/CVI                |    |

| Driver functions                                   |    |

| Delphi (Pascal) Programming Interface              |    |

| Type definition                                    |    |

| Include Driver                                     |    |

| Examples                                           |    |

| Driver functions                                   |    |

| Visual Basic Programming Interface                 |    |

| Include Driver                                     |    |

| Visual Basic Examples                              |    |

| VBA for Excel Examples                             |    |

| Driver functions                                   | 34 |

| Programming the Board                             |    |

|---------------------------------------------------|----|

| Overview                                          |    |

| Register tables                                   |    |

| Programming examples                              |    |

| Error handling                                    |    |

| Initialization                                    |    |

| Starting the automatic initialization routine     |    |

| PCI Register                                      |    |

| Hardware version                                  |    |

| Date of production                                |    |

| Serial number                                     |    |

| Maximum possible sample rate                      |    |

| Installed memory                                  |    |

| Installed features and options                    |    |

| Used interrupt line                               |    |

| Used type of driver                               |    |

| Powerdown and reset                               |    |

| Analog Inputs                                     | 41 |

| Channel Selection                                 |    |

| Important note on channels selection              |    |

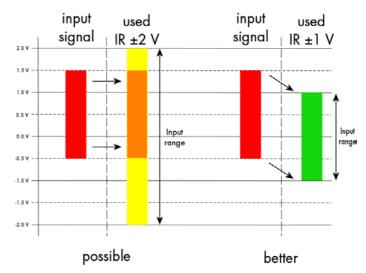

| Setting up the inputs                             |    |

| Input ranges                                      |    |

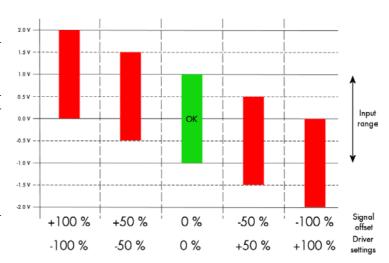

| Input offset                                      |    |

| Input termination                                 | 44 |

| Automatical adjustment of the offset settings     |    |

| Standard acquisition modes                        | ΛΕ |

| General Information                               |    |

|                                                   |    |

| Programming                                       |    |

| Memory, Pre- and Posttrigger                      |    |

| Starting without interrupt (classic mode)         |    |

| Data organization                                 |    |

|                                                   |    |

| Sample format                                     |    |

| •                                                 |    |

| FIFO Mode                                         |    |

| Overview                                          |    |

| General Information                               |    |

| Background FIFO Read                              |    |

| Speed Limitations                                 |    |

| Programming                                       |    |

| Software Buffers                                  |    |

| Buffer processing                                 |    |

| FIFO mode                                         |    |

| Example FIFO acquisition mode                     |    |

| Data organization                                 |    |

| Sample format                                     |    |

| Clock generation                                  | 54 |

| Overview                                          |    |

| Internally generated sample rate                  |    |

| Standard internal sample rate                     |    |

| Using plain quartz with no PLL                    |    |

| Direct external clock                             |    |

| External clock with divider                       |    |

|                                                   |    |

| rigger modes and appendant registers              |    |

| General Description                               |    |

| Software trigger                                  |    |

| External TTL trigger                              |    |

| Edge triggers                                     |    |

| Pulsewidth triggers                               |    |

| Channel Trigger                                   |    |

| Overview of the channel trigger registers         |    |

| Triggerlevel                                      |    |

| Detailed description of the channel trigger modes | 65 |

| Option Multiple Recording                                                                                                                               | 73 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Recording modes                                                                                                                                         |    |

| Standard Mode                                                                                                                                           |    |

| FIFO Mode                                                                                                                                               | 73 |

| Trigger modes                                                                                                                                           | 73 |

| Option Gated Sampling                                                                                                                                   | 75 |

| Recording modes                                                                                                                                         |    |

| Standard Mode                                                                                                                                           |    |

| FIFO Mode                                                                                                                                               | 75 |

| Trigger modes                                                                                                                                           |    |

| General information and trigger delay                                                                                                                   |    |

| Allowed trigger modes                                                                                                                                   |    |

| Example program                                                                                                                                         | 77 |

| Option Timestamp                                                                                                                                        | 78 |

| General information                                                                                                                                     | 78 |

| Timestamp modes                                                                                                                                         | 78 |

| Standard mode                                                                                                                                           | 78 |

| StartReset mode                                                                                                                                         |    |

| RefClock mode (optional)                                                                                                                                |    |

| Timestamp Status                                                                                                                                        |    |

| Reading out timestamp data                                                                                                                              |    |

| Functions for accessing the data                                                                                                                        |    |

| Data format                                                                                                                                             |    |

| Example programs                                                                                                                                        |    |

| Standard acquisition mode                                                                                                                               |    |

| Acquisition with Multiple Recording                                                                                                                     |    |

| Option Extra I/O                                                                                                                                        |    |

| Digital I/Os                                                                                                                                            |    |

| Channel direction                                                                                                                                       |    |

| Transfer Data                                                                                                                                           |    |

| Analog Outputs                                                                                                                                          |    |

| Programming example                                                                                                                                     |    |

| Synchronization (Option)                                                                                                                                |    |

| The different synchronization options                                                                                                                   |    |

| Synchronization with option cascading                                                                                                                   |    |

| Synchronization with option starhub                                                                                                                     |    |

| The setup order for the different synchronization options                                                                                               | 83 |

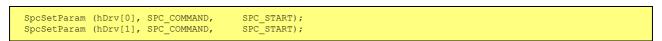

| Setup Order for use with standard (non FIFO) mode and equally clocked boards<br>Setup synchronization for use with FIFO mode and equally clocked boards |    |

| Additions for synchronizing different boards                                                                                                            |    |

| Additions for equal boards with different sample rates                                                                                                  |    |

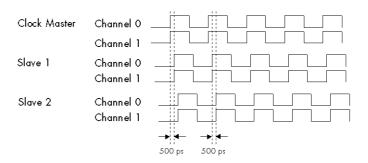

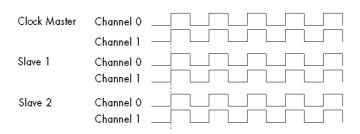

| Resulting delays using different boards or speeds                                                                                                       | 93 |

|                                                                                                                                                         |    |

| Appendix Error Codes                                                                                                                                    |    |

| Pin assignment of the multipin connector                                                                                                                |    |

| Extra I/O with external connector(Option -XMF)                                                                                                          | 93 |

| Pin assignment of the multipin cable                                                                                                                    |    |

| Pin assignment of the internal multipin connector.                                                                                                      |    |

| Extra I/O with internal connector (Option -XIO)                                                                                                         |    |

|                                                                                                                                                         | 70 |

Preface Introduction

# **Introduction**

## **Preface**

This manual provides detailed information on the hardware features of your Spectrum instrumentation board. This information includes technical data, specifications, block diagram and a connector description.

In addition, this guide takes you through the process of installing your board and also describes the installation of the delivered driver package for each operating system.

Finally this manual provides you with the complete software information of the board and the related driver. The reader of this manual will be able to integrate the board in any PC system with one of the supported bus and operating systems.

Please note that this manual provides no description for specific driver parts such as those for LabVIEW or MATLAB. These drivers are provided by special order.

For any new information on the board as well as new available options or memory upgrades please contact our webside http://www.spectrum-instrumentation.com. You will also find the current driver package with the latest bug fixes and new features on our site.

Please read this manual carefully before you install any hardware or software. Spectrum is not responsible for any hardware failures resulting from incorrect usage.

# **General Information**

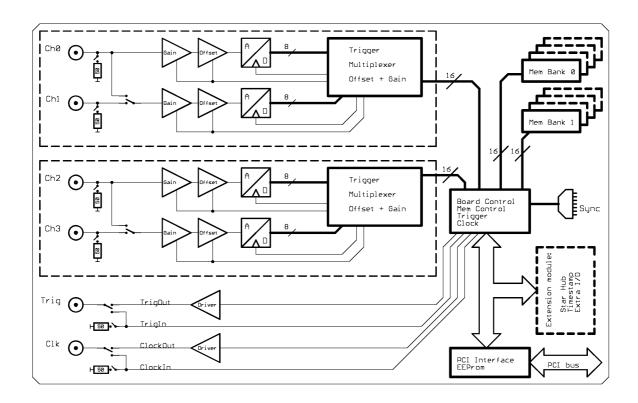

The 4 models of the MI.20xx series are designed for the fast and high quality data acquisition. Every of the up to four input channels has its own A/D converter and it's own programmable input amplifier.

This allows to record signals with 8 bit resolution without any phase delay between them. The inputs could be selected to one of seven input ranges by software and could be programmed to compensate an input offset of  $\pm 400\%$  of the input range. The extremely large on-board memory allows long time recording even with highest sample rates. A FIFO mode is also integrated on the board. This allows to record data continuously and to process it in the PC or to store it to hard disk.

Several boards of the MI.xxxx series may be connected together by the internal standard synchronisation bus to work with the same time base.

Application examples: Laboratory equipment, Supersonics, LDA/PDA, Radar, Spectroscopy, production test.

# Different models of the MI.20xx series

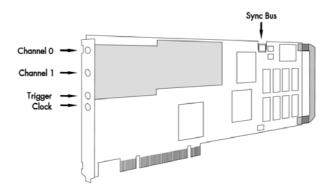

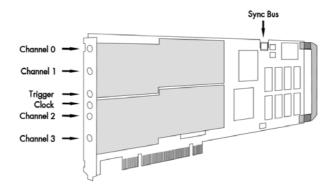

The following overwiew shows the different available models of the MI.20xx series. They differ in the number mounted generation modules and the number of available channels. You can also see the model dependant allocation of the output connectors.

- MI.2020

- MI.2030

•

- MI.2021

- MI.2031

Additional options Introduction

# **Additional options**

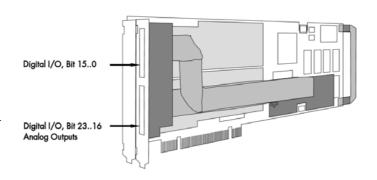

### Extra I/O (Option -XMF)

With this simple-to-use enhancement it is possible to control a wide range of external instruments or other equipment. Therefore you have 24 digital I/O and the 4 analog outputs available.

The asynchronous I/Os of the extra I/O option are useful if an external amplifier should be controlled, any kind of signal source must be programmed, an antenna must be adjusted, a status information from external machine has to be obtained or different test signals have to be routed to the board.

The additional inputs and outputs are mounted on an extra bracket.

The figure shows the allocation of the two connectors.

The shown option is mounted exemplarily on a board with two modules. Of course you can also combine this option as well with a board that is equipped with only one module.

It is not possible to use this option together with the star hub or timestamp option, because there is just space for one piggyback module on the on-board expansion slot.

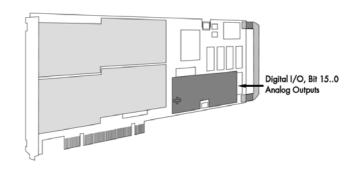

# Extra I/O (Option -XIO)

With this simple-to-use enhancement it is possible to control a wide range of external instruments or other equipment. Therefore you have 16 digital I/O and the 4 analog outputs available.

The asynchronous I/Os of the extra I/O option are useful if an external amplifier should be controlled, any kind of signal source must be programmed, an antenna must be adjusted, a status information from external machine has to be obtained or different test signals have to be routed to the board.

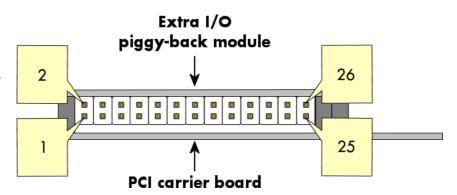

The additional inputs and outputs are not mounted on an extra brak-

ket, but are available on an internal connector. The figure shows the position of this connector on the bottom side of the extra I/O piggy-back module.

The shown option is mounted exemplarily on a board with two modules. Of course you can also combine this option as well with a board that is equipped with only one module.

It is not possible to use this option together with the star hub or timestamp option, because there is just space for one piggyback module on the on-board expansion slot.

Introduction Additional options

## **Starhub**

The star hub module allows the synchronisation of up to 16 Ml boards. It is possible to synchronise boards of the same type with each other as well as different types.

The module acts as a star hub for clock and trigger signals. Each board is connected with a small cable of the same length, even the master board. That minimises the clock skew between the different boards. The figure shows the piggyback module mounted on the base board schematically without any cables to achieve a better visibility.

Any board could be the clock master and the same or any other

board could be the trigger master. All trigger modes that are available on the master board are also available if the synchronisation star hub is used.

The cable connection of the boards is automatically recognised and checked by the driver at load time. So no care must be taken on how to cable the boards. The programming of the star hub is included in the standard board interface and consists of only 3 additional commands.

It is not possible to use this option together with the timestamp or extra I/O option, because the is just space for one piggyback module on the on-board expansion slot.

### <u>Timestamp</u>

The timestamp module was designed to record the exact time information between trigger events.

The timestamp reset command sets an internal counter to zero. The counter is running with the same resolution as the sample rate. On each trigger event a timestamp is recorded in an extra FIFO. The recorded timestamps are read out asynchronously to the board sampling.

If the absolute time information is of interest it is possible to synchronise the timestamp counter with a 1 Hz "seconds" signal of a radio clock or a GPS receiver. In that case the 64 bit timestamp information is split up

in two parts. The one part counts the number of seconds starting with the reset command, the other part is set to zero on every rising edge of the seconds signal and specifies the exact time position in relation to the seconds signal.

The figure shows the piggyback module installed on the on-board expansion slot. The shown option is mounted exemplarily on a board with two modules.

It is not possible to use this option together with the star hub or extra I/O option, because the is just space for one piggyback module on the on-board expansion slot.

The Spectrum type plate Introduction

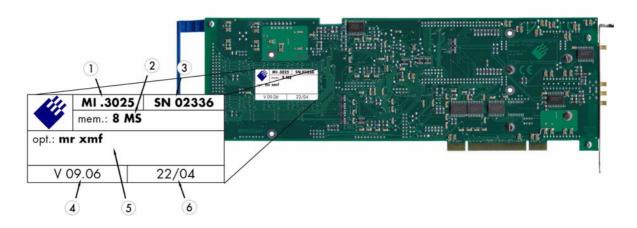

# The Spectrum type plate

The Spectrum type plate, which consists of the following components, can be found on all of our boards.

- 1 The board type, consisting of the two letters describing the bus (in this case MI for the PCI bus) and the model number.

- 2 The size of the on-board installed memory in MSamples. In this example there are 8 MS (16 MByte) installed.

- 3 The serial number of your Spectrum board. Every board has a unique serial number.

- 4) The board revision, consisting of the base version and the module version.

- A list of the installed options. A complete list of all available options is shown in the order information. In this example the options 'Multiple recording' and 'Extra I/O with external outputs' are installed.

- 6 The date of production, consisting of the calendar week and the year.

Please always supply us with the above information, especially the serial number in case of support request. That allows us to answer your questions as soon as possible. Thank you.

Introduction Hardware information

# **Hardware information**

# **Block diagram**

# **Technical Data**

| Resolution                          | 8 bit                                                                                                                                                                     | Dimension                                | 312 mm x 107 mm                                                                                                    |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Differential linearity error (ADC)  | 0.5 LSB typ.                                                                                                                                                              | Width (Standard)                         | 1 full size slot                                                                                                   |

| Integral linearity error (ADC)      | 0.5 LSB typ.                                                                                                                                                              | Width (with star hub option)             | 2 full size slots                                                                                                  |

| Multi: Trigger to 1st sample delay  | fixed                                                                                                                                                                     | Analogue Connector                       | 3 mm SMB male                                                                                                      |

| Multi: Recovery (re-arm) time       | < 20 samples                                                                                                                                                              | Overvoltage protection (range < ±500 mV) | ±5 V                                                                                                               |

| Trigger accuracy 2/4 channel mode   | 1 Sample                                                                                                                                                                  | Overvoltage protection (range > ±500 mV) | ±50 V                                                                                                              |

| Trigger accuracy 1 channel mode     | 2 Samples                                                                                                                                                                 | Warm up time                             | 10 minutes                                                                                                         |

| Ext. clock: delay to internal clock | 42 ns ± 2 ns                                                                                                                                                              | Operating temperature                    | 0°C - 50°C                                                                                                         |

| input signal with 50 ? termination  | max 5 V rms                                                                                                                                                               | Storage temperature                      | -10°C - 70°C                                                                                                       |

| Trigger output delay                | 1 Sample                                                                                                                                                                  | Humidity                                 | 10% to 90%                                                                                                         |

| Input impedance                     | 50 Ohm / 1 MOhm    25 pF                                                                                                                                                  |                                          |                                                                                                                    |

| Min internal clock                  | 1 kS/s                                                                                                                                                                    | Power consumption 5 V @ full speed       | max 3.4 A (17.0 Watt)                                                                                              |

| Min external clock                  | 1 MS/s                                                                                                                                                                    | Power consumption 5 V @ power down       | max 1.9 A (9.5 Watt)                                                                                               |

| Trigger input:Standard TTL level    | Low: $0.5$ > level < $0.8$ V<br>High: $2.0$ V > level < $5.5$ V<br>Trigger pulse must be valid $\geq 2$ clock periods.                                                    | Clock input: Standard TTL level          | Low: -0.5 > level < 0.8 V<br>High: 2.0 V > level < 5.5 V<br>Rising edge is used.<br>Required duty cycle: 50% ± 5%  |

| Trigger output                      | Standard TTL, capable of driving 50 Ohm.<br>Low < 0.4 V (@ 20 mA, max 64 mA)<br>High > 2.4 V (@ -20 mA, max -32 mA)<br>One positive edge after the first internal trigger | Clock output                             | Standard TTL, capable of driving 50 Ohm<br>Low < 0.4 V (@ 20 mA, max 64 mA)<br>High > 2.4 V (@ -20 mA, max -32 mA) |

| Input range                                  | ±50 mV                          | ±100 mV   | ±200 mV   | ±500 mV           | ±1 V      | ±2 V      | ±5 V      |

|----------------------------------------------|---------------------------------|-----------|-----------|-------------------|-----------|-----------|-----------|

| Software programmable offset                 | ±200 mV                         | ±400 mV   | ±800 mV   | ±2 V              | ±4 V      | ±8 V      | ±20 V     |

| Offset error                                 |                                 |           | < 11      | LSB, adjustable b | y user    |           |           |

| Gain error                                   | < 2 %                           | < 2 %     | < 2 %     | < 2 %             | < 2 %     | < 2 %     | < 2 %     |

| MI.202x: Noise (rms): 50 Ohm, 50 MS/s        | < 0.5 LSB                       | < 0.5 LSB | < 0.5 LSB | < 0.5 LSB         | < 0.5 LSB | < 0.5 LSB | < 0.5 LSB |

| MI.203x: Noise (rms): 50 Ohm, 100/200 MS/s   | < 2.0 LSB                       | < 1.5 LSB | < 1.0 LSB | < 1.0 LSB         | < 1.0 LSB | < 1.0 LSB | < 1.0 LSB |

| Crosstalk 5 MHz signal, ±50 mV input, 50 Ohm | Hz signal, ±50 mV input, 50 Ohm |           |           | •                 |           |           |           |

Hardware information Introduction

|                    | MI.2020<br>MI.2021 | MI.2030<br>MI.2031 |

|--------------------|--------------------|--------------------|

| max internal clock | 50 MS/s            | 200 MS/s           |

| max external clock | 50 MS/s            | 100 MS/s           |

| -3 dB bandwidth    | > 25 MHz           | > 90 MHz           |

# **Dynamic Parameters**

|                        | MI.2020<br>MI.2021 | MI.2030<br>MI.2031 |

|------------------------|--------------------|--------------------|

| Test - Samplerate      | 50 MS/s            | 100 MS/s           |

| Testsignal frequency   | 1 MHz              | 1 MHz              |

| SNR (typ)              | > 47.5 dB          | > 45.9 dB          |

| THD (typ)              | < -52.5 dB         | < -49.1 dB         |

| SFDR (typ), incl harm. | > 57.0 dB          | > 55.5 dB          |

| SINAD (typ)            | > 46.0 dB          | > 44.2             |

| ENOB (based on SINAD)  | > 7.3              | > 7.1              |

Dynamic parameters are measured at ± 1 V input range (if no other range is stated) and 50 Ohm termination with the samplerate specified in the table. Measured parameters are averaged 20 times to get typical values. Test signal is a pure sine wave of the specified frequency with > 99% amplitude. SNR and RMS noise parameters may differ depending on the quality of the used PC. SNR = Signal to Noise Ratio, THD = Total Harmonic Distortion, SFDR = Spurious Free Dynamic Range, SINAD = Signal Noise and Distortion, ENOB = Effective Number of Bits. For a detailed description please see application note 002.

# **Order information**

| Order No      | Description                                                       | Order No    | Description                                                   |

|---------------|-------------------------------------------------------------------|-------------|---------------------------------------------------------------|

| MI2020        | MI.2020 with 16 MSample memory and drivers/SBench 5.x             | MI2xxx-32M  | Option: 32 MSample memory instead of 16 MSample standard mem  |

| MI2021        | MI.2021 with 16 MSample memory and drivers/SBench 5.x             | MI2xxx-64M  | Option: 64 MSample memory instead of 16 MSample standard mem  |

| MI2030        | MI.2030 with 16 MSample memory and drivers/SBench 5.x             | MI2xxx-128M | Option: 128 MSample memory instead of 16 MSample standard mem |

| MI2031        | MI.2031 with 16 MSample memory and drivers/SBench 5.x             | MI2xxx-256M | Option: 256 MSample memory instead of 16 MSample standard mem |

|               |                                                                   | MI2xxx-512M | Option: 512 MSample memory instead of 16 MSample standard mem |

| MI2xxx-smod   | Star Hub: Synchronisation of 2 - 16 boards, one option per system | MI2xxx-up   | Additional handling costs for later memory upgrade            |

| Mlxxxx.xio    | Extra I/O, internal connector: 16 DI/O, 4 Analog out              |             |                                                               |

| Mlxxxx-xmf    | Extra I/O, external connector: 24 DI/O, 4 Analog out, incl. cable | MI2xxx-mr   | Option Multiple Recording: Memory segmentation                |

| MI2xxx-time   | Timestamp option: Extra memory for trigger time                   | MI2xxx-gs   | Option Gated Sampling: Gate signal controls acquisition       |

|               |                                                                   | MI2xxx-cs   | Synchronisation of 2 - 4 boards, one option per system        |

| Cab-3f-9m-80  | Adapter cable: SMB female to BNC male 80 cm                       |             |                                                               |

| Cab-3f-9m-200 | Adapter cable: SMB female to BNC male 200 cm                      | MI20xx-dl   | DASYLab driver for MI.20xx series                             |

| Cab-3f-9f-80  | Adapter cable: SMB female to BNC female 80 cm                     | MI20xx-hp   | VEE driver for MI.20xx series                                 |

| Cab-3f-9f-200 | Adapter cable: SMB female to BNC female 200 cm                    | MI20xx-lv   | LabVIEW driver for MI.20xx series                             |

|               |                                                                   | MATLAB      | MATLAB driver for all MI.xxxx, MC.xxxx and MX.xxxx series.    |

Hardware Installation System Requirements

# **Hardware Installation**

# **System Requirements**

All Spectrum MI.xxxx instrumentation boards are compliant to the PCI standard and require in general one free full length slot. Depending on the installed options additional free slots can be necessary.

# **Warnings**

#### **ESD Precautions**

The boards of the MI.xxxx series contain electronic components that can be damaged by electrostatic discharge (ESD).

Before installing the board in your system or even before touching it, it is absolutely necessary to bleed of any electrostatic electricity.

### **Cooling Precautions**

The boards of the MI.xxxx series operate with components having very high power consumption at high speeds. For this reason it is absolutely required to cool this board sufficiently. It is strongly recommended to install an additional cooling fan producing a stream of air across the boards surface. In most cases professional PC-systems are already equipped with sufficient cooling power. In that case please make sure that the air stream is not blocked.

During longer pauses between the single measurements the power down mode should be called to reduce the heat production.

#### Sources of noise

The boards of the MI.xxxx series should be placed far away from any noise producing source (like e.g. the power supply). It should especially be avoided to place the board in the slot directly adjacent to another fast board (like the graphics controller).

# Installing the board in the system

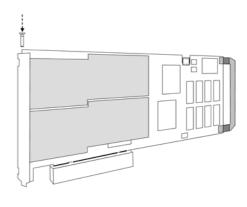

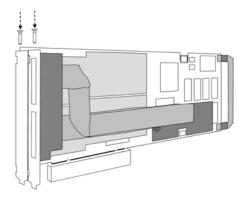

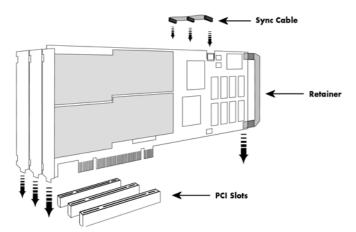

### Installing a single board without any options

Before installing the board you first need to unscrew and remove the dedicated blind-bracket usually mounted to cover unused slots of your PC. Please keep the screw in reach to fasten your Spectrum board afterwards. All Spectrum boards require a full length PCI slot with a track at the backside to guide the board by it's retainer. Now insert the board slowly into your computer. This is done best with one hand each at both fronts of the board.

While inserting the board take care not to tilt the retainer in the track.

Please be very carefully when inserting the board in the PCI slot, as most of the mainboards are mounted with spacers and therefore might be damaged if they are exposed to high preasure.

After the board's insertion fasten the screw of the bracket carefully, without overdoing.

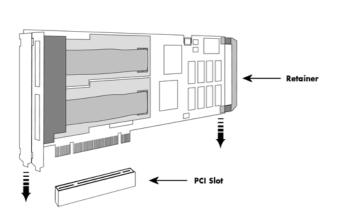

### Installing a board with digital inputs/outputs

Before installing the board you first need to unscrew and remove the dedicated blind-brackets usually mounted to cover unused slots of your PC. Please keep the screws in reach to fasten your Spectrum board and the extra bracket afterwards. All Spectrum boards require a full length PCI slot with a track at the backside to guide the board by it's retainer. Now insert the board and the extra bracket slowly into your computer. This is done best with one hand each at both fronts of the board.

While inserting the board take care not to tilt the retainer in the track.

Please be very carefully when inserting the board in the PCI slot, as most of the mainboards are mounted with spacers and therefore might be damaged they are exposed to high preasure.

After the board's insertion fasten the screws of both brackets carefully, without overdoing. The figure shows an example of a board with two installed modules

# Installing a board with extra I/O (Option -XMF)

Before installing the board you first need to unscrew and remove the dedicated blind-brackets usually mounted to cover unused slots of your PC. Please keep the screws in reach to fasten your Spectrum board and the extra bracket afterwards. All Spectrum boards require a full length PCI slot with a track at the backside to guide the board by it's retainer. Now insert the board and the extra bracket slowly into your computer. This is done best with one hand each at both fronts of the board.

While inserting the board take care not to tilt the retainer in the track.

Please be very carefully when inserting the board in the PCI slot, as most of the mainboards are mounted with spacers and therefore might be damaged they are exposed to high preasure.

After the board's insertion fasten the screws of both brackets carefully, without overdoing. The figure shows an example of a board with two installed modules.

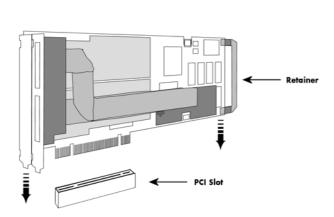

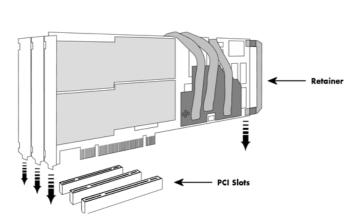

# Installing multiple boards synchronized by starhub

#### Hooking up the boards

Before mounting several synchronized boards for a multi channel system into the PC you can hook up the boards with their synchronization cables first. If there is enough space in your computer's case (e.g. a big tower case) you can also mount the boards first and hook them up afterwards. Spectrum ships the boards together with the needed amount of synchronization cables. All of them are matched to the same length, to achieve a zero clock delay between the boards.

#### Only use the included flat ribbon cables.

All of the boards, including the board that carrys the starhub piggy-back module, must be wired to the starhub as the figure is showing exemplarily for three synchronized boards.

It does not matter which of the 16 connectors on the starhub module you use for which board. The software driver will detect the types and order of the synchronized boards automatically. The figure shows the three cables mounted next to each other only to achieve a better visibility.

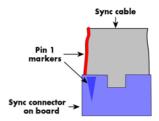

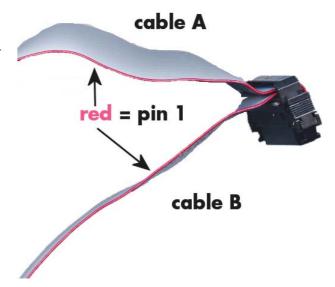

As some of the synchronization cables are not secured against wrong plugging you should take care to have the pin 1 markers on the multiple connectors and the cable on the same side, as the figure on the right is showing.

#### Mounting the wired boards

Before installing the boards you first need to unscrew and remove the dedicated blind-brackets usually mounted to cover unused slots of your PC. Please keep the screws in reach to fasten your Spectrum boards afterwards. All Spectrum boards require a full length PCI slot with a track at the backside to guide the board by it's retainer. Now insert the board and the extra bracket slowly into your computer. This is done best with one hand each at both fronts of the board. Please keep in mind that the board carrying the starhub piggy-back module requires the width of two slots.

While inserting the boards take care not to tilt the retainers in the tracks.

Please be very carefully when inserting the boards in the PCI slots, as most of the mainboards are mounted with spacers and therefore might be damaged if they are exposed to high preasure.

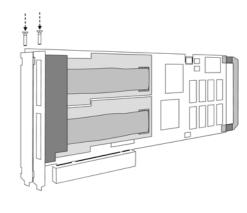

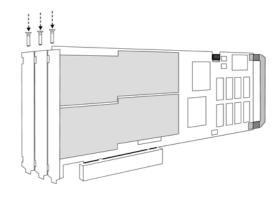

After the boards insertion fasten the screws of all brackets carefully, without overdoing. The figure shows an example of three boards with two installed modules.

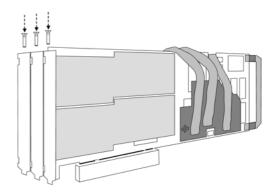

# **Installing multiple synchronized boards**

#### Hooking up the boards

Before mounting several synchronized boards for a multi channel system into the PC you can hook up the boards with the synchronization cable first. If there is enough space in your computer's case (e.g. a big tower case) you can also mount the boards first and hook them up afterwards. Spectrum ships the boards together with the needed synchronization cable.

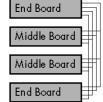

All of the possible four boards must be wired with the delivered synchronization cable. The figure is showing an example of three synchronized boards.

The outer boards have a soldered termination for the sync bus. These boards are marked with an additional sticker.

Only mount the cluster of synchronized boards in a row with the dedicated boards on the outer sides.

#### Mounting the wired boards

Before installing the boards you first need to unscrew and remove the dedicated blind-brackets usually mounted to cover unused slots of your PC. Please keep the screws in reach to fasten your Spectrum boards afterwards. All Spectrum boards require a full length PCI slot with a track at the backside to guide the board by it's retainer. Now insert the boards slowly into your computer. This is done best with one hand each at both fronts of the board.

While inserting the boards take care not to tilt the retainers in the tracks.

Please be very carefully when inserting the boards in the PCI slots, as most of the mainboards are mounted with spacers and therefore might be damaged if they are exposed to high preasure.

After the boards insertion fasten the screws of all brackets carefully, without overdoing. The figure shows an example of three boards with two installed modules.

Software Driver Installation Interrupt Sharing

# **Software Driver Installation**

Before using the board a driver must be installed that matches the operating system. The installation is done in different ways depending on the used operating system. The driver that is on CD supports all boards of the MI, MC and MX series. That means that you can use the same driver for all boards of theses families.

# **Interrupt Sharing**

This board uses a PCI interrupt for DMA data transfer and for controlling the FIFO mode. The used interrupt line is allocated by the PC BIOS at system start and is normally depending on the selected slot. Because there is only a limited number of interrupt lines available on the PCI bus it can happen that two or more boards must use the same interrupt line. This so called interrupt sharing must be supported by all drivers of the participating equipment.

Most available drivers and also the Spectrum driver for your board can manage interrupt sharing. But there are also some drivers on the market that can only use one interrupt exclusively. If this equipment shares an interrupt with the Spectrum board, the system will hang up if the second driver is loaded (the time is depending on the operating system).

If this happens it is necessary to reconfigure the system in that way that the critical equipment has an exclusive access to an interrupt.

On most systems the BIOS shows a list of all installed PCI boards with their allocated interrupt lines directly after system start. You have to check whether an interrupt line is shared between two boards. Some BIOS allow the manual allocation of interrupt lines. Have a look in your mainboard manual for further information on this topic.

Because normally the interrupt line is fixed for one PCI slot it is simply necessary to use another slot for the critical board to force a new interrupt allocation. You have to search a configuration where all critical boards have only exclusive access to one interrupt.

Depending on the system, using the Spectrum board with a shared interrupt may degrade performance a little. Each interrupt needs to be checked by two drivers. For this reason when using time critical FIFO mode even the Spectrum board should have an exclusively access to one interrupt line.

Windows 98 Software Driver Installation

# Windows 98

## **Installation**

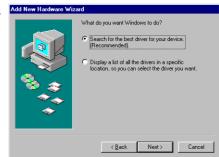

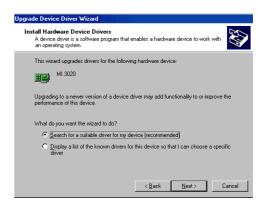

When installing the board in a Windows 98 system the Spectrum board will be recognized automatically on the next start-up.

The system offers the direct installation of a driver for the board.

Let Windows search automatically for the best driver for your system.

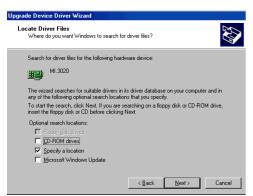

Select the CD that was delivered with the board as installation source. The driver files are located on CD in the directory

\Driver\Win98\_2k\_XP.

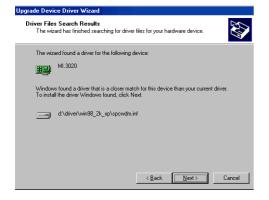

The hardware assistant shows you the exact board type that has been found like the MI.3020 in the example. Older boards (before june 2004) show "Spectrum Board" instead.

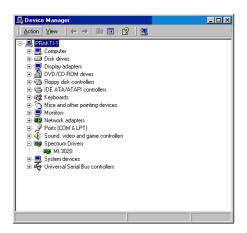

The drivers can be used directly after installation. It is not necessary to restart the system. The installed drivers are linked in the device manager. Below you'll see how to examine the driver version and how to update the driver with a newer version.

# **Version control**

If you want to check which driver version is installed in the system this can be easily done in the device manager. Therefore please start the device manager from the control panel and show the properties of the installed driver.

On the property page Windows 98 shows the date of the driver.

Software Driver Installation Windows 98

After clicking the driver info button the detailed version information of the driver is shown. In the case of a support question this information must be presented together with the board's serial number to the support team to help finding a fast solution.

## **Driver - Update**

If a new driver version is to be installed no Spectrum board should be in use. So please stop and exit all software that could access the boards. New drivers are available at http://www.spectrum-instrumentation.com. After down loading the driver unzip it to a temporary folder.

A new driver version is directly installed from the device manager. Therefore please open the properties page of the driver as shown in the section before. As next step click on the update driver button and follow the steps of the driver installation in a similar way to the previous board and driver installation.

Please select the path where the new driver version was unzipped to. If you've got the new driver version on CD please select the \Driver\Win98\_2k\_XP path on the CD containing the new driver ver-

sion.

The new driver version can be used directly after installation without restarting the system. Please keep in mind to update the driver of all installed Spectrum boards.

Windows 2000 Software Driver Installation

# Windows 2000

### **Installation**

When installing the board in a Windows 2000 system the Spectrum board will be recognized automatically on the next start-up.

The system offers the direct installation of a driver for the board.

Let Windows search automatically for the best driver for your system.

Select the CD that was delivered with the board as installation source. The driver files are located on CD in the directory

\Driver\Win98\_2k\_XP.

The hardware assistant shows you the exact board type that has been found like the MI.3020 in the example. Older boards (before june 2004) show "Spectrum Board" instead.

The drivers can be used directly after installation. It is not necessary to restart the system. The installed drivers are linked in the device manager.

Below you'll see how to examine the driver version and how to update the driver with a newer version.

#### **Version control**

If you want to check which driver version is installed in the system this can be easily done in the device manager. Therefore please start the device manager from the control panel and show the properties of the installed driver.

On the property page Windows 2000 shows the date and the version of the installed driver.

After clicking the driver details button the detailed version information of the driver is shown. In the case of a support question this information must be presented together with the board's serial number to the support team to help finding a fast solution.

Software Driver Installation Windows 2000

# **Driver - Update**

If a new driver version should be installed no Spectrum board is allowed to be in use by any software. So please stop and exit all software that could access the boards.

A new driver version is directly installed from the device manager. Therefore please open the properties page of the driver as shown in the section before. As next step click on the update driver button and follow the steps of the driver installation in a similar way to the previous board and driver installation.

Please select the path where the new driver version was unzipped to. If you've got the new driver version on CD please select the \Driver\Win98\_2k\_XP path on the CD containing the new driver version.

The new driver version can be used directly after installation without restarting the system. Please keep in mind to update the driver of all installed Spectrum boards.

Windows XP Software Driver Installation

# Windows XP

## **Installation**

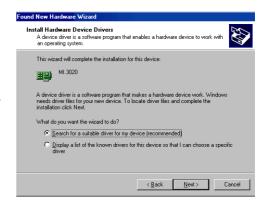

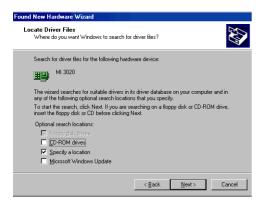

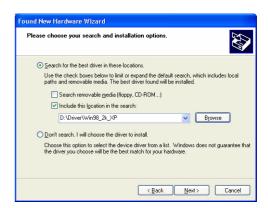

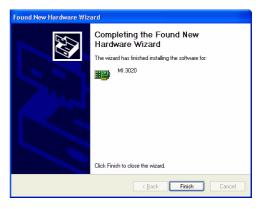

When installing the board in a Windows XP system the Spectrum board will be recognized automatically on the next start-up.

The system offers the direct installation of a driver for the board.

Do not let Windows automatically search for the best driver, because sometimes the driver will not be found on the CD. Please take the option of choosing a manual installation path instead.

Allow Windows XP to search for the most suitable driver in a specific directory. Select the CD that was delivered with the board as installation source. The driver files are located on CD in the directory \Driver\Win98\_2k\_XP.

Welcome to the Found New Hardware Wizard

If your hardware came with an installation CD or floppy disk, insert it now.

< Back Next > Cancel

Install from a list or specific location (Advanced)

This wizard helps you install software for

What do you want the wizard to do?

Click Next to continue

PCI Device

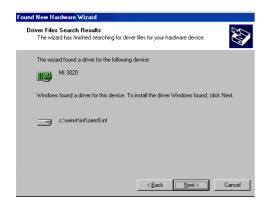

The hardware assistant shows you the exact board type that has been found like the MI.3020 in the example. Older boards (before june 2004) show "Spectrum Board" instead.

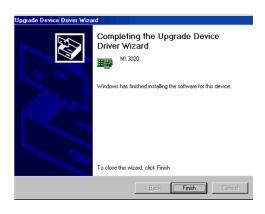

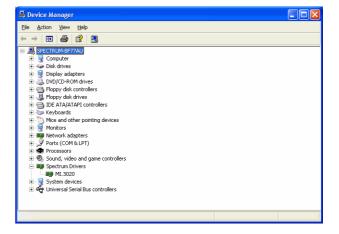

The drivers can be used directly after installation. It is not necessary to restart the system. The installed drivers are linked in the device manager.

Below you'll see how to examine the driver version and how to update the driver with a newer version.

### **Version control**

If you want to check which driver version is installed in the system this can be easily done in the device manager. Therefore please start the device manager from the control panel and show the properties of the installed driver.

Software Driver Installation Windows XP

On the property page Windows XP shows the date and the version of the installed driver.

After clicking the driver details button the detailed version information of the driver is shown. In the case of a support question this information must be presented together with the board's serial number to the support team to help finding a fast solution.

## **Driver - Update**

If a new driver version should be installed no Spectrum board is allowed to be in use by any software. So please stop and exit all software that could access the boards.

A new driver version is directly installed from the device manager. Therefore please open the properties page of the driver as shown in the section before. As next step click on the update driver button and follow the steps of the driver installation in a similar way to the previous board and driver installation.

Please select the path where the new driver version was unzipped to. If you've got the new driver version on CD please select the  $\Driver\Win98_2k_XP$  path on the CD containing the new driver version.

Please choose your search and installation options.

Search for the best driver in these locations.

Hardware Update Wizard

The new driver version can be used directly after installation without restarting the system. Please keep in mind to update the driver of all installed Spectrum boards.

Use the check boxes below to limit or expand the default search, which includes local paths and removable media. The best driver found will be installed.

Windows NT Software Driver Installation

# Windows NT

## **Installation**

Under Windows NT the Spectrum driver must be installed manually. The driver is found on CD in the directory \Install\WinNTDrv. Please start the "Setup.exe" program. The installation is performed totally automatically, simply click on the "Next" button. After installtion the system must be rebooted once (see picture on the right side). The driver is install to support one PCI/PXI or CompactPCI

device. If more boards are installed in the system the configuration of the driver has to be changed. Please see the following chapter for this topic.

# Adding boards to the Windows NT driver

The Windows NT driver must be configured by the Driver Configuration utility to support more than one board. The Driver Configuration utility is automatically installed with the driver. The Utility can be found in the start menu as "DrvConfig".

To add a new card please follow these steps:

- Increase the board number on top of the screen by pressing the right button

- Change the board type from "Not Installed" to "PCI Board"

- Press the "Apply changes" button

- Press the "OK" button

- Restart the system

### **Driver - Update**

If a new driver version should be installed no Spectrum board is allowed to be in use by any software. So please stop and exit all software that could access the boards.

When updating a system please simply execute the setup file of the new driver version. Afterwards the system has to be rebooted. The driver configuration is not changed.

Software Driver Installation Linux

# Linux

#### **Overview**

The Spectrum boards are delivered with drivers for linux. It is necessary to install them manually following the steps explained afterwards. The linux drivers can be found on CD in the directory / Driver/linux. As linux is an open source operating system there are several distributions in use world-wide that are compiled with different kernel settings. As we are not able to install and maintain hundreds of different distributions and versions we had to focus on some common used linux distributions.

However if your distribution does not work with one of these pre-compiled kernel modules or you have a specialized kernel installed (like a SMP kernel) you can get the linux driver sources directly from us. With this sources it's no problem to compile and use the linux driver on your system. Please contact your local distributor to get the sources. The Spectrum linux drivers are compatible with kernel versions 2.4 and 2.6.

On this CD you'll find pre-compiled linux kernel modules for the following versions:

```

SuSE version 8.0 Kernel 2.4.18 directory / Driver/linux/suse80 SuSE version 8.2 Kernel 2.4.20 directory / Driver/linux/suse82 SuSE version 9.0 Kernel 2.4.21 directory / Driver/linux/suse90 SuSE version 9.1 Kernel 2.6.4 directory / Driver/linux/suse91 Redhat version 9.0 Kernel 2.4.20 directory / Driver/linux/redhat90

```

### Installation

#### Loain as root.

It is necessary to have the root rights for installing a driver.

#### Select the right driver from the CD.

Refer to the list shown above. If your distribution is not listed there please select the module that most closely matches your installed kernel version. Copy the driver kernel module spc.o from the CD directory to your hard disk. Be sure to use a hard disk directory that is a accessible by all users who should work with the board.

#### First time load of the driver

The linux driver is shipped as the loadable module spc.o. The driver includes all Spectrum PCI, PXI and CompactPCI boards. The boards are recognized automatically after driver loading.Load the driver with the insmod command:

```

linux:~ # insmod spc.o

```

The insmod command may generate a warning that the driver module was compiled for another kernel version. In that case you may try to load the driver module with the force parameter and test the board very carefully.

```

linux:~ # insmod -f spc.o

```

If the kernel module could not be loaded in your linux installation it is necessary to compile the driver directly on your system. Please contact-Spectrum to get the needed source files including the compilation description.

Depending on the used linux distribution the insmod command generates a message telling the driver version and the board types and serial numbers that have been found. If your distribution does not show this message it is possible to view them with the dmesg command:

```

linux:~ # dmesg

... some other stuff

spc driver version: 3.07 build 0

sp0: MI.3020 sn 01234

```

In the example we show you the output generated by a MI.3020. All other board types are similar to this output but showing the correct board type.

#### **Examine the major number of the driver**

For accessing the device driver it is necessary to know the major number of the device. This number is listed in the /proc/devices list. The device driver is called "spec" in this list. Normally this number is 254 but this depends on the device drivers that have been installed before.

```

linux:~ # cat /proc/devices

Character devices:

...

171 ieee1394

180 usb

188 ttyUSB

254 spec

Block devices:

1 ramdisk

2 fd

...

```

Linux Software Driver Installation

#### **Installing the device**

You connect a device to the driver with the mknod command. The major number is the number of the driver as shown in the last step, the minor number is the index of the board starting with 0. This step must only be done once for the system where the boards are installed in. The device will remain in the file structure even if the board is de-installed from the system.

The following command makes a device for the first Spectrum board the driver has found:

```

linux:~ # mknod /dev/spc0 c 254 0

```

Make sure that the users who work with the driver have full rights access for the device. Therefore you should give all persons all rights to the device:

```

linux:~ # chmod a+w /dev/spc0

```

Now it is possible to access the board using this device.

#### **Driver info**

Information about the installed boards could be found in the /proc/spectrum file. All PCI, PXI and CompactPCI boards show the basic information found in the EEProm there. This is an example output generated by a MI.3020:

### **Automatic load of the driver**

It is necessary to load the kernel driver module after each start of the system before using the boards. Therefore you may add the "insmod spc.o" command in one of the start-up files. Or you may load the kernel driver module manually whenever you need access to the board.

Software Software Overview

# **Software**

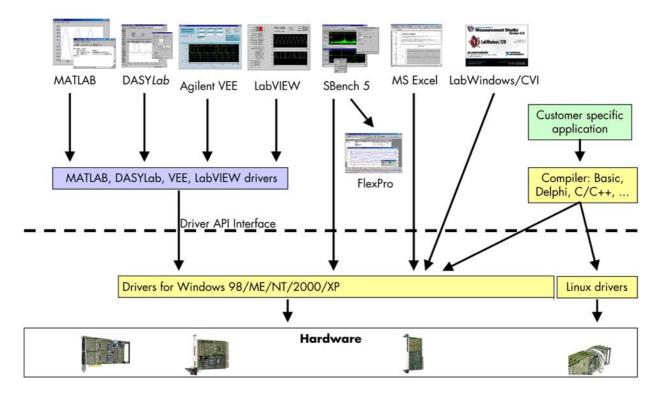

This chapter gives you an overview about the structure of the drivers and the software, where to find and how to use the examples. It detailed shows how the drivers are included under different programming languages and where the differences are when calling the driver functions from different programming languages.

This manual only shows the use of the standard driver API. For further information on programming drivers for third-party software like LabVIEW, MATLAB, DASYLab or VEE an additional manual is required that is delivered with the ordered driver option.

### **Software Overview**

The Spectrum drivers offer you a common and fast API for using all of the board hardware features. This API is nearly the same on all operating systems. Based on this API one can write your own programs using any programming language that can access the driver API. This manual detailed describes the driver API allowing you to write your own programs.

The optional drivers for third-party products like LabVIEW or DASYLab are also based on this API. The special functionality of these drivers is not subject of this manual and is described on separate manuals delivered with the driver option.

# First Test with SBench

After installation of the board and the drivers it can be useful to first test the board function with a ready to run software before starting with programming. A full version of SBench 5.x is delivered with the board on CD. The program supports all actual acquisition, generator and digital I/O boards from Spectrum. Depending on the used board and the software setup, one could use SBench as a digital storage oscilloscope, a spectrum analyser, a logic analyser or simply as a data recording front end. Different export and import formats allow the use of SBench together with a variety of other programs.

On the CD you'll find an install version of SBench in the directory /Install/SBench. There's also a pre-installed program version on CD that can be started directly from CD without installing to hard disk. This file can be found in the /Programs/SBench5 directory. Also on CD is a program description that shows in detail how SBench works and what settings have to be done to use SBench in one of the different modes. The manual is found in the path /Internet/english/swmanuals/SBench.

The current version of SBench can be down loaded free of charge directly from the Spectrum website http://www.spectrum-instrumentation.com. Please go to the download section and get the latest version there.

SBench is designed to run under Windows 98, Windows ME, Windows NT, Windows 2000 and Windows XP. It does not run under Linux. At the moment there is no graphical ready-to-run software for Linux available. Please use the driver examples to examine whether the board is correctly installed under Linux.

C/C++ Driver Interface Software

# C/C++ Driver Interface

C/C++ is the main programming language for which the drivers have been build up. Therefore the interface to C/C++ is the best match. All the small examples of the manual showing different parts of the hardware programming are done with C.

### **Header files**

The basic task before using the driver is to include the header files that are delivered on CD together with the board. The header files are found in the directory /Driver/header\_c. Please don't change them in any way because they are updated with each new driver version to include the new registers and new functionality.

Includes the platform specific definitions for data types and function declarations. All data types are based on this definitions. The use of this typ definition file allows the use of examples and programs on different platforms without changes to the program source. dlltyp.h

Defines all registers and commands which are used in the Spectrum driver for the different boards. The registers a board uses are described in the board speregs.h

cific part of the documentation.

Defines the functions of the driver. All definitions are taken from the file dlltyp.h. The functions itself are described below. spectrum.h

Lists all and describes all error codes that can be given back by any of the driver functions. The error codes and their meaning are described in detail in the spcerr.h

errors.h Only there for backward compatibility with older program versions. Please use spcerr.h instead.

Example for including the header files:

```

// ---- driver includes ---- #include "dlltyp.h"

#include "spectrum.h'

#include "spcerr.h"

#include "regs.h

```

### Microsoft Visual C++

#### **Include Driver**

The driver files can be easily included in Microsoft C++ by simply using the library file that is delivered together with the drivers. The library file can be found on the CD in the path /Driver/Win98\_2k\_YP. Please include the library file Spectrum.lib in your Visual C++ project. All functions described below are now available in your program.

#### **Examples**

Examples can be found on CD in the path /Examples/vc. There is one subdirectory for each board family. You'll find board specific examples for that family there. The examples are bus type independent. As a result that means that the MI30xx directory contains examples for the MI.30xx, the MC.30xx and the MX.30xx families. The example directories contain a running project file for Microsoft Visual C++ that can be directly loaded and compiled.

There are also some more board independent examples in the directory MIxxxx. These examples show different aspects of the boards like programming options or synchronization and have to be combined with one of the board specific example.

### Linux Gnu C

#### **Include Driver**

The interface of the linux drivers is a little bit different from the windows interface. To make the access easier and to have more similar examples we added an include file that re maps the standard driver functions to the linux specific functions. This include file is found in the path / Examples/linux/spcioctl.inc. All examples are based on this file.

Example for including Linux driver:

```

// ---- driver includes -----

#include "dlltyp.h'

#include "regs.h"

#include "errors.h"

// ---- include the easy ioctl commands from the driver ---- \# include \ ".../spcioctl.inc"

```

#### **Examples**

Examples can be found on CD in the path /Examples/linux. There is one subdirectory for each board family. You'll find board specific examples for that family there. The examples are bus type independent. As a result that means that the MI30xx directory contains examples for the MI.30xx, the MC.30xx and the MX.30xx families. The examples are simple one file programs and can be compiled using the Gnu C compiler gcc. It's not necessary to use a makefile for them.

Software C/C++ Driver Interface

# Other Windows C/C++ compilers

#### **Include Driver**

To access the driver, the driver functions must be loaded from the driver dll. This can be easily done by standard windows functions. There is one example in the directory /Examples/other that shows the process. After loading the functions from the dll one can proceed with the examples that are given for Microsoft Visual C++.

Example of function loading:

```

// definition of external function that has to be loaded from DLL

typedef int16 (SPCINITPCIBOARDS) (int16* pnCount, int16* pnPCIVersion);

typedef int16 (SPCSETPARAM)

(int16 nNr, int32 lReg, int32 lValue);

typedef int16 (SPCGETPARAM)

(int16 nNr, int32 lReg, int32* plValue);

SPCINITPCIBOARDS* pfnSpcInitPCIBoards;

SPCSETPARAM*

pfnSpcSetParam;

pfnSpcGetParam;

// ---- Search for dll -----

hDLL = LoadLibrary ("spectrum.dll");

---- Load functions from DLL --

pfnSpcInitPCIBoards = (SPCINITPCIBOARDS*) GetProcAddress (hDLL, "SpcInitPCIBoards");

GetProcAddress (hDLL, "SpcSetParam");

pfnSpcSetParam =

(SPCSETPARAM*)

pfnSpcGetParam =

(SPCGETPARAM*)

GetProcAddress (hDLL, "SpcGetParam");

```

# **National Instruments LabWindows/CVI**

#### **Include Drivers**

To use the Spectrum driver under LabWindows/CVI it is necessary to first load the functions from the driver dll. This is more or less similar to the above shown process with the only difference that LabWindows/CVI uses it's own library handling functions instead of the windows standard functions.

Example of function loding under LabWindows/CVI:

```

// ---- load the driver entries from the DLL ----

DriverId = LoadExternalModule ("spectrum.lib");

// ---- Load functions from DLL ----

SpcInitPCIBoards = (SPCINITPCIBOARDS*) GetExternalModuleAddr (DriverId, "SpcInitPCIBoards", &Status);

SpcSetParam = (SPCSETPARAM*) GetExternalModuleAddr (DriverId, "SpcSetParam", &Status);

SpcGetParam = (SPCGETPARAM*) GetExternalModuleAddr (DriverId, "SpcGetParam", &Status);

```

#### **Examples**

Examples for LabWindows/CVI can be found on CD in the directory /Examples/cvi. Theses examples show mainly how to include the driver in a LabWindows/CVI environment and don't use any special functions of the boards. The examples have to be merged with the standard windows examples described under Visual C++.

#### **Driver functions**

The driver contains five functions to access the hardware.

#### **Function SpcInitPCIBoard**

This function initializes all installed PCI, PXI and CompactPCI boards. The boards are recognized automatically. All installation parameters are read out from the hardware and stored in the driver. The number of PCI boards will be given back in the value Count and the version of the PCI bus itself will be given back in the value PCIVersion.

Function SpcInitPCIBoards:

```

int16 SpcInitPCIBoards (int16* count, int16* PCIVersion);

```

Under Linux this function is not available. Instead one must open and close the driver with the standard file functions open and close. The functionality behind this function is the same as the SpcInitPCIBoards function.

Using the Driver under Linux:

```

hDrv = open ("/dev/spc0", O_RDWR);

...

close (hDrv);

```

C/C++ Driver Interface Software

#### **Function SpcSetParam**

All hardware settings are based on software registers that can be set by the function SpcSetParam. This function sets a register to a defined value or executes a command. The board must first be initialized. The available software registers for the driver are listed in the board specific part of the documentation below.

The value "nr" contains the index of the board that you want to access, the value "reg" is the register that has to be changed and the value "value" is the new value that should be set to this software register. The function will return an error value in case of malfunction.

Function SpcSetParam

int16 SpcSetParam (int16 nr, int32 reg, int32 value);

Under Linux the value "nr" must contain the handle that was retrieved by the open function for that specific board. The values is then not of the type "int16" but of the type "handle".

#### **Function SpcGetParam**

The function SpcGetParam reads out software registers or status information. The board must first be initialized. The available software registers for the driver are listed in the board specific part of the documentation below.

The value "nr" contains the index of the board that you want to access, the value "reg" is the register that has to be read out and the value "value" is a pointer to a value that should contain the read parameter after function call. The function will return an error value in case of malfunction.

Function SpcGetParam

int16 SpcGetParam (int16 nr, int32 reg, int32\* value);

Under Linux the value "nr" must contain the handle that was given back by the open function of that specific board. The values is then not of the type "int16" but of the type "handle".

#### Function SpcSetData

Writes data to the board for a specific memory channel. The board must first be initialized. The value "nr" contains the index of the board that you want to access, the "ch" parameter contains the memory channel. "start" and "len" define the position of data to be written. "data" is a pointer to the array holding the data. The function will return an error value in case of malfunction.

This function is only available on generator or i/o boards. The function is not available on acquisition boards.

Function SpcSetData (Windows)

int16 SpcSetData (int16 nr, int16 ch, int32 start, int32 len, dataptr data);

Under Linux the additional parameter nBytesPerSample must be used for this function. For all boards with 8 bit resolution the parameter is "1", for all boards with 12, 14 or 16 bit resolution this parameter has to be "2". Under Linux the value "hDrv" must contain the handle that was given back by the open function of that specific board.

Function SpcSetData (Linux)

int32 SpcSetData (int hDrv, int32 1Ch, int32 1Start, int32 1Len, int16 nBytesPerSample, dataptr pvData)

#### Function SpcGetData

Reads data from the board from a specific memory channel. The board must first be initialized. The value "nr" contains the index of the board that you want to access, the "ch" parameter contains the memory channel. "start" and "len" define the position of data to be read. "data" is a pointer to the array that should hold the data. The function will return an error value in case of malfunction.

This function is only available on acquisition or i/o boards. The function is not available on generator boards.

Function SpcGetData

int16 SpcGetData (int16 nr, int16 ch, int32 start, int32 len, dataptr data);

Software C/C++ Driver Interface

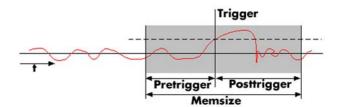

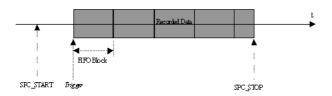

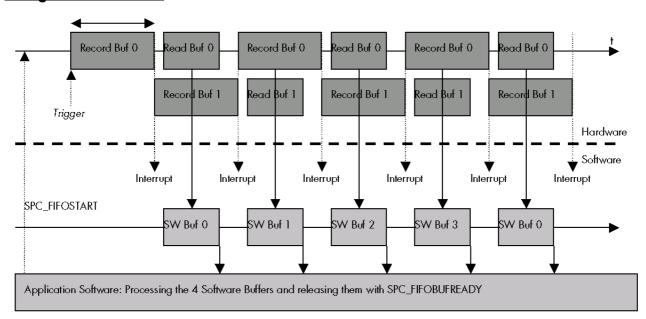

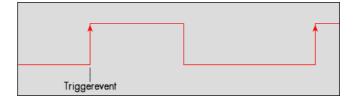

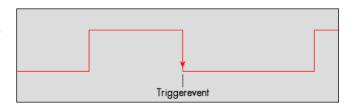

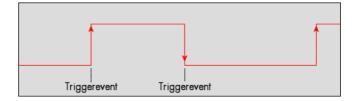

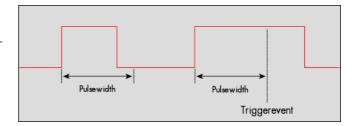

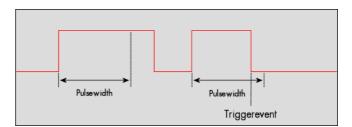

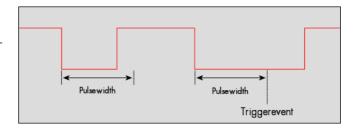

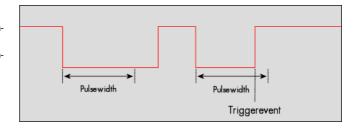

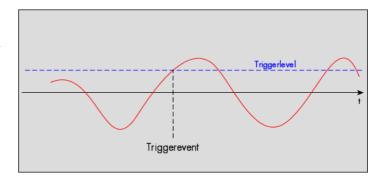

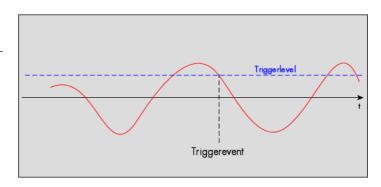

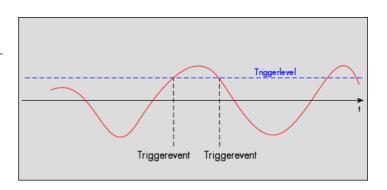

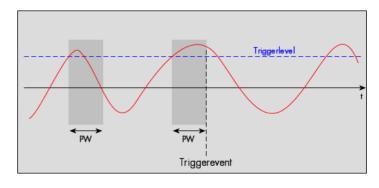

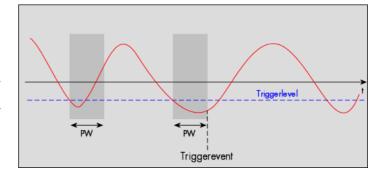

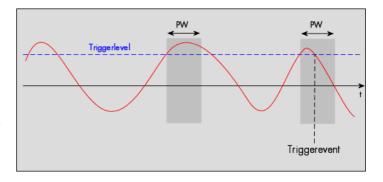

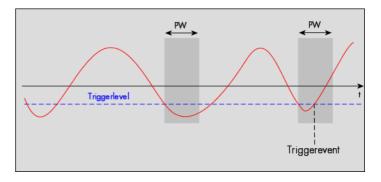

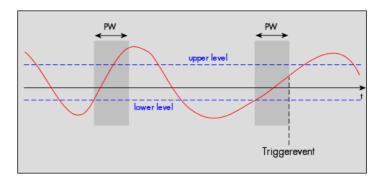

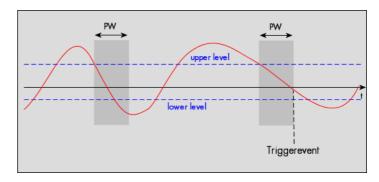

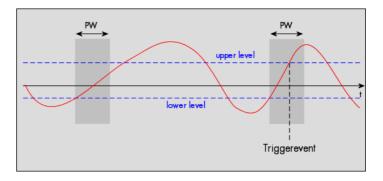

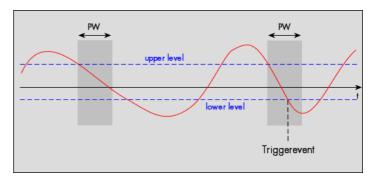

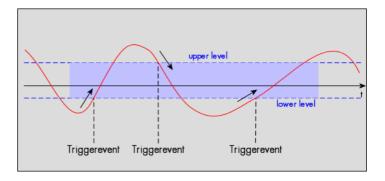

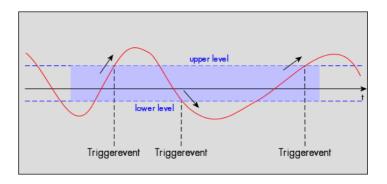

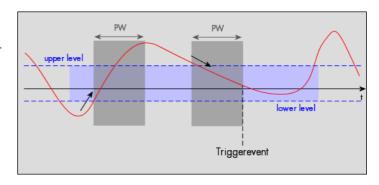

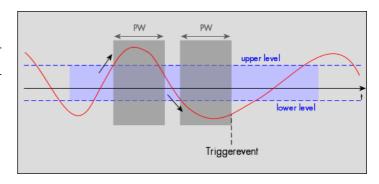

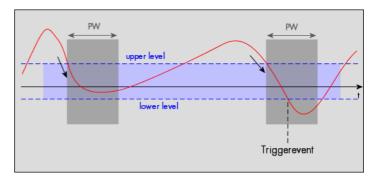

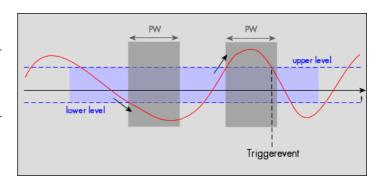

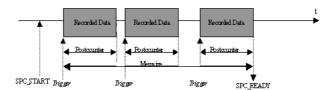

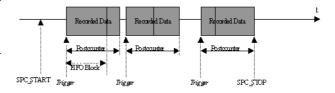

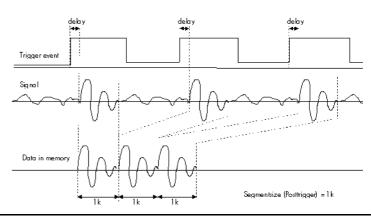

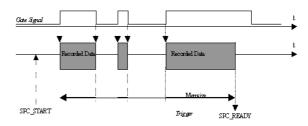

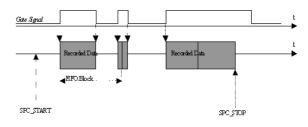

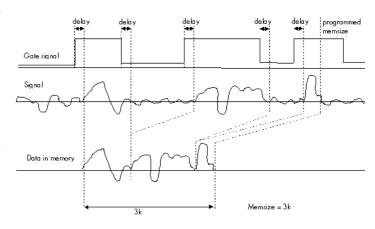

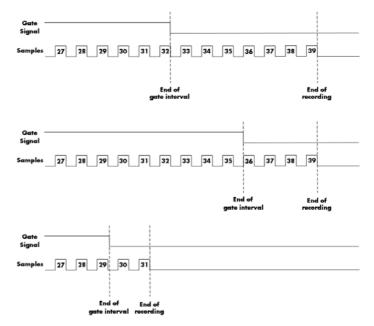

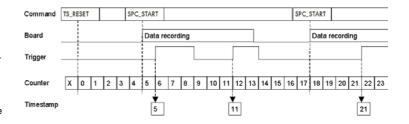

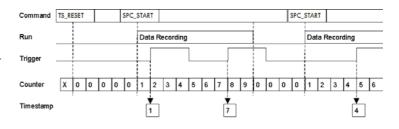

Under Linux the additional parameter nBytesPerSample must be used for this function. For all boards with 8 bit resolution the parameter is "1", for all boards with 12, 14 or 16 bit resolution this parameter has to be "2". Under Linux the value "hDrv" must contain the handle that was given back by the open function of that specific board.